CDP1821C3 Overview

Description

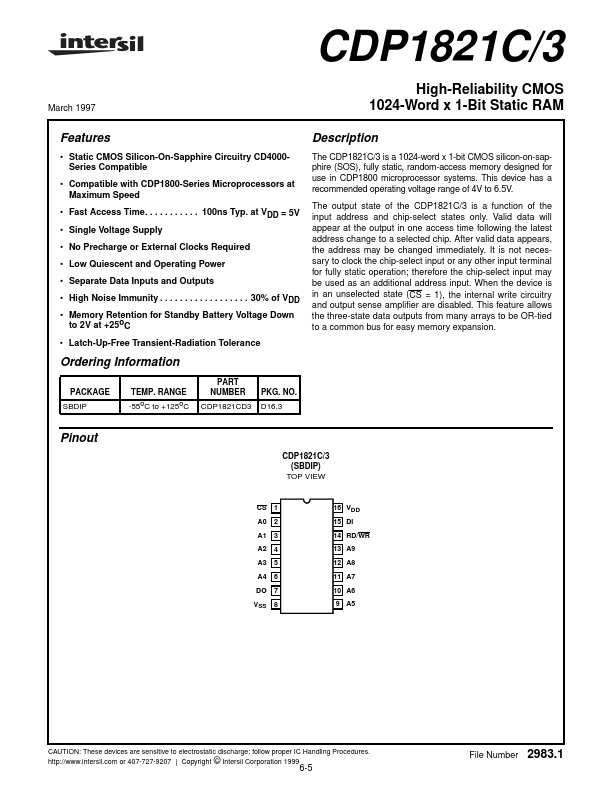

The CDP1821C/3 is a 1024-word x 1-bit CMOS silicon-on-sapphire (SOS), fully static, random-access memory designed for use in CDP1800 microprocessor systems. This device has a recommended operating voltage range of 4V to 6.5V.

Key Features

- Static CMOS Silicon-On-Sapphire Circuitry CD4000Series Compatible

- Compatible with CDP1800-Series Microprocessors at Maximum Speed

- Fast Access Time. . . . . . . . . . . 100ns Typ. at VDD = 5V

- Single Voltage Supply

- No Precharge or External Clocks Required

- Low Quiescent and Operating Power

- Separate Data Inputs and Outputs

- High Noise Immunity . . . . . . . . . . . . . . . . . . 30% of VDD

- Memory Retention for Standby Battery Voltage Down to 2V at +25oC

- Latch-Up-Free Transient-Radiation Tolerance