CD4517BMS

Overview

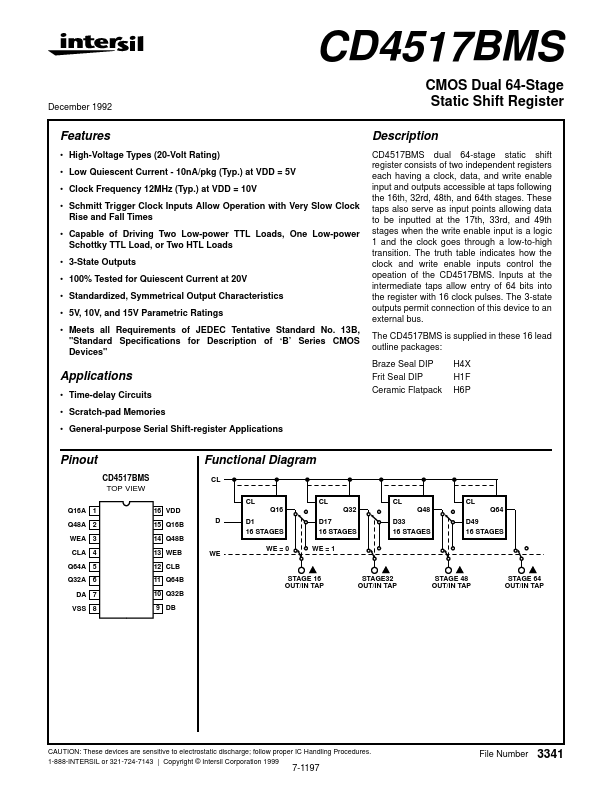

CD4517BMS dual 64-stage static shift register consists of two independent registers each having a clock, data, and write enable input and outputs accessible at taps following the 16th, 32rd, 48th, and 64th stages. These taps also serve as input points allowing data to be inputted at the 17th, 33rd, and 49th stages when the write enable input is a logic 1 and the clock goes through a low-to-high transition.

- High-Voltage Types (20-Volt Rating)

- Low Quiescent Current - 10nA/pkg (Typ.) at VDD = 5V

- Clock Frequency 12MHz (Typ.) at VDD = 10V

- Schmitt Trigger Clock Inputs Allow Operation with Very Slow Clock Rise and Fall Times

- Capable of Driving Two Low-power TTL Loads, One Low-power Schottky TTL Load, or Two HTL Loads

- 3-State Outputs

- 100% Tested for Quiescent Current at 20V

- Standardized, Symmetrical Output Characteristics

- 5V, 10V, and 15V Parametric Ratings

- Meets all Requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of ‘B’ Series CMOS Devices"