CD4029BMS

Overview

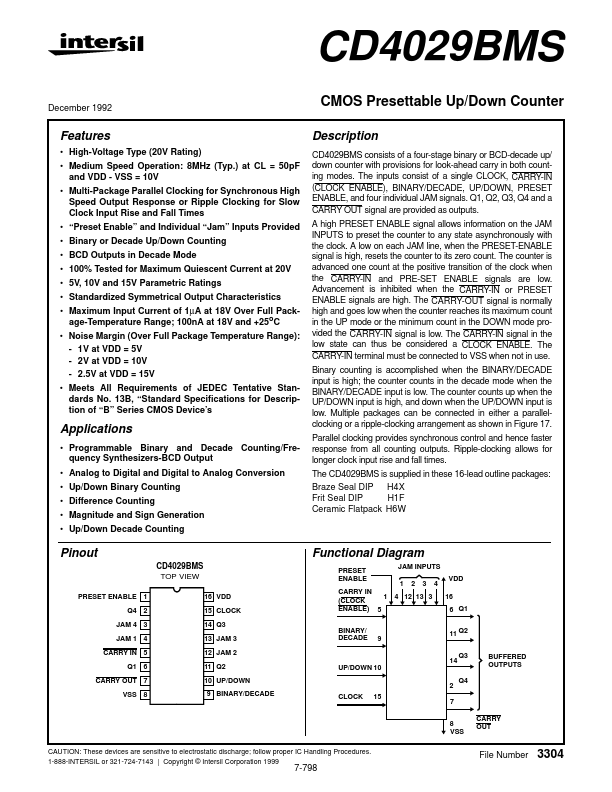

CD4029BMS consists of a four-stage binary or BCD-decade up/ down counter with provisions for look-ahead carry in both counting modes. The inputs consist of a single CLOCK, CARRY-IN (CLOCK ENABLE), BINARY/DECADE, UP/DOWN, PRESET ENABLE, and four individual JAM signals.

- High-Voltage Type (20V Rating)

- Medium Speed Operation: 8MHz (Typ.) at CL = 50pF and VDD - VSS = 10V

- Multi-Package Parallel Clocking for Synchronous High Speed Output Res