CD4018BMS Overview

Description

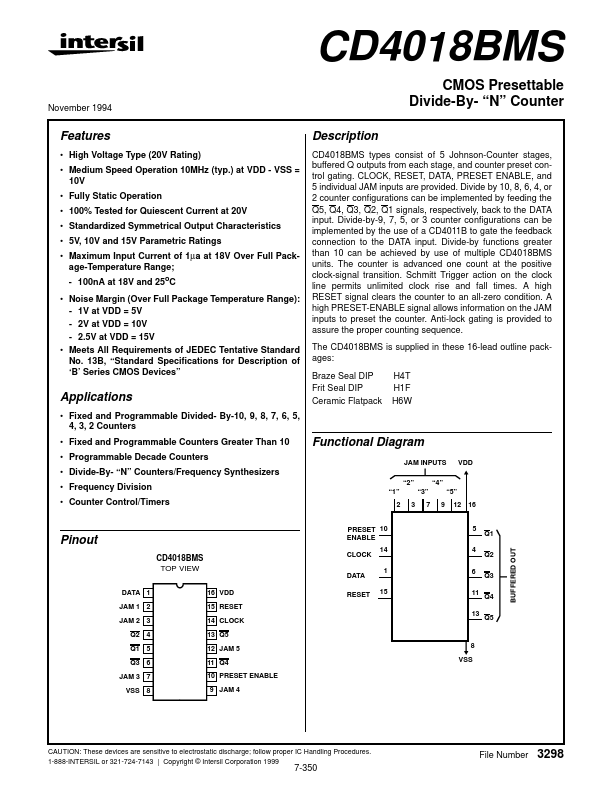

CD4018BMS types consist of 5 Johnson-Counter stages, buffered Q outputs from each stage, and counter preset control gating. CLOCK, RESET, DATA, PRESET ENABLE, and 5 individual JAM inputs are provided.

Key Features

- High Voltage Type (20V Rating)

- Medium Speed Operation 10MHz (typ.) at VDD

- Fully Static Operation

- 100% Tested for Quiescent Current at 20V

- Standardized Symmetrical Output Characteristics

- 5V, 10V and 15V Parametric Ratings

- Maximum Input Current of 1µa at 18V Over Full Package-Temperature Range

- 100nA at 18V and 25oC

- Noise Margin (Over Full Package Temperature Range)

- 1V at VDD = 5V