CD4011BT

Overview

- QML Class T, Per MIL-PRF-38535

- Radiation Performance - Gamma Dose (γ) 1 x 105 RAD(Si) - SEP Effective LET > 75 MEV/gm/cm2

- Propagation Delay Time = 60ns (typ.) at CL = 50pF, VDD = 10V

- Buffered Inputs and Outputs

- Standardized Symmetrical Output Characteristics

- 100% Tested for Maximum Quiescent Current at 20V Specifications Specifications for Rad Hard QML devices are controlled by the Defense Supply Center in Columbus (DSCC). The SMD numbers listed below must be used when ordering. Detailed Electrical Specifications for the CD4011BT are contained in SMD 5962-96621. A “hot-link” is provided from our website for downloading. Intersil’s Quality Management Plan (QM Plan), listing all Class T screening operations, is also available on our website.

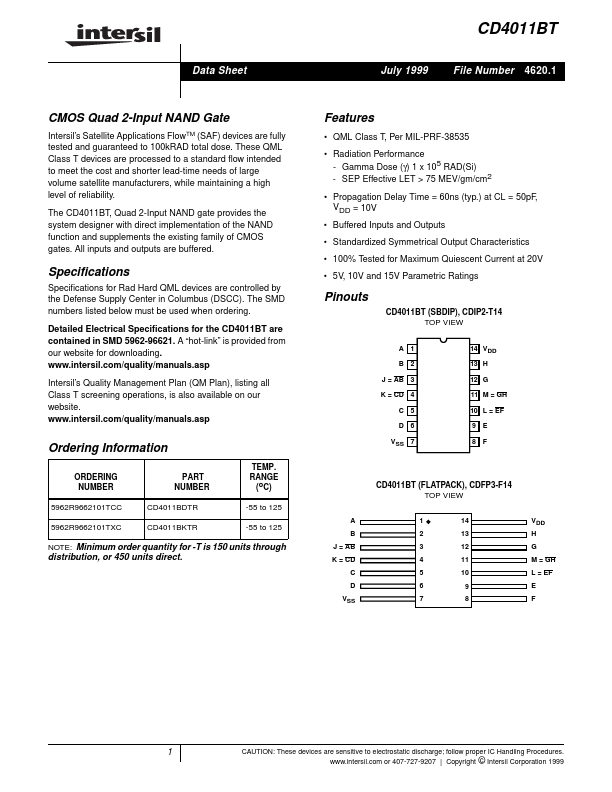

- 5V, 10V and 15V Parametric Ratings Pinouts