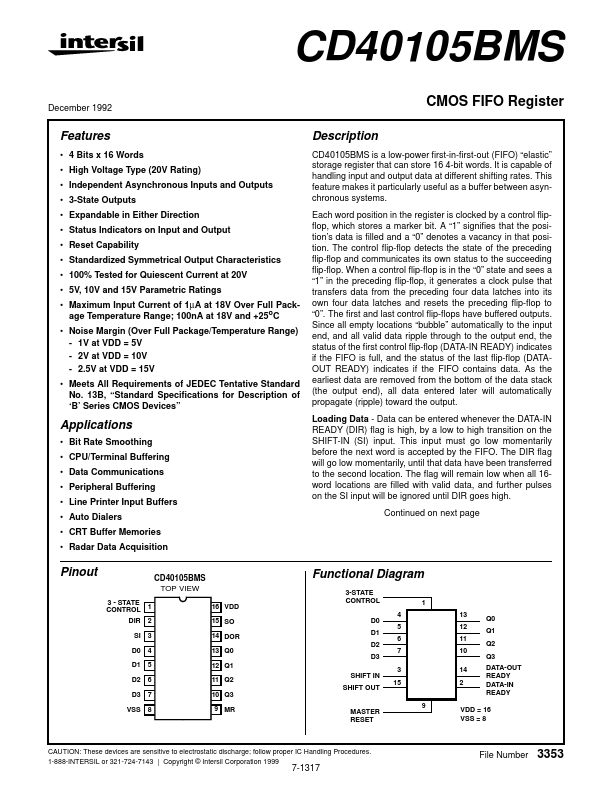

| Part | CD40105BMS |

|---|---|

| Description | CMOS FIFO Register |

| Manufacturer | Intersil |

| Size | 116.54 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| CD40105B | RCA | CMOS FIFO Register |

| CD40105BF | Texas Instruments | CMOS FIFO Register |

| CD40105BE | Texas Instruments | CMOS FIFO Register |

| CD40105B | Texas Instruments | CMOS FIFO Register |

| CD40105BF3A | Texas Instruments | CMOS FIFO Register |