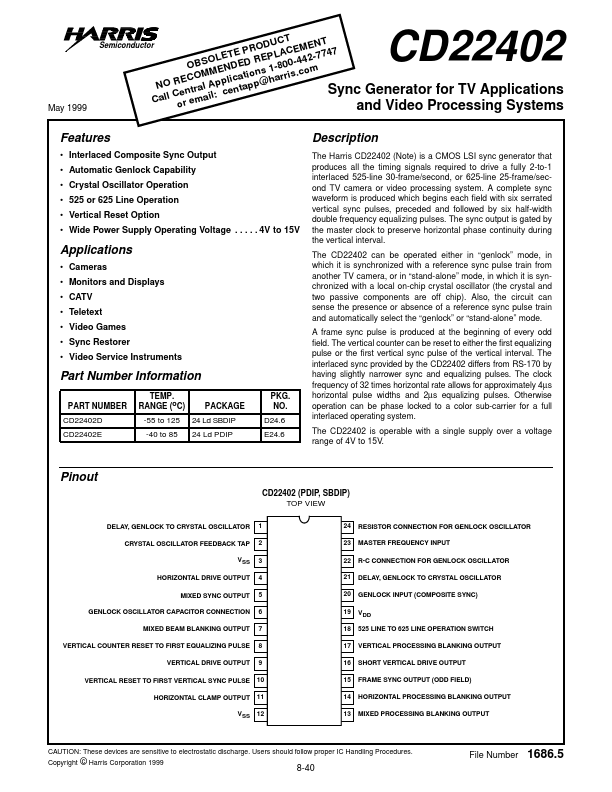

CD22402

Description

The Harris CD22402 (Note) is a CMOS LSI sync generator that produces all the timing signals required to drive a fully 2-to-1 interlaced 525-line 30-frame/second, or 625-line 25-frame/second TV camera or video processing system. A complete sync waveform is produced which begins each field with six serrated vertical sync pulses, preceded and followed by six half-width double frequency equalizing pulses.

Key Features

- Interlaced Composite Sync Output

- Automatic Genlock Capability

- Crystal Oscillator Operation

- 525 or 625 Line Operation

- Vertical Reset Option