PF48F3000P0ZTQ0 Overview

Key Specifications

Package: FBGA

Pins: 88

Operating Voltage: 1.8 V

Max Voltage (typical range): 2 V

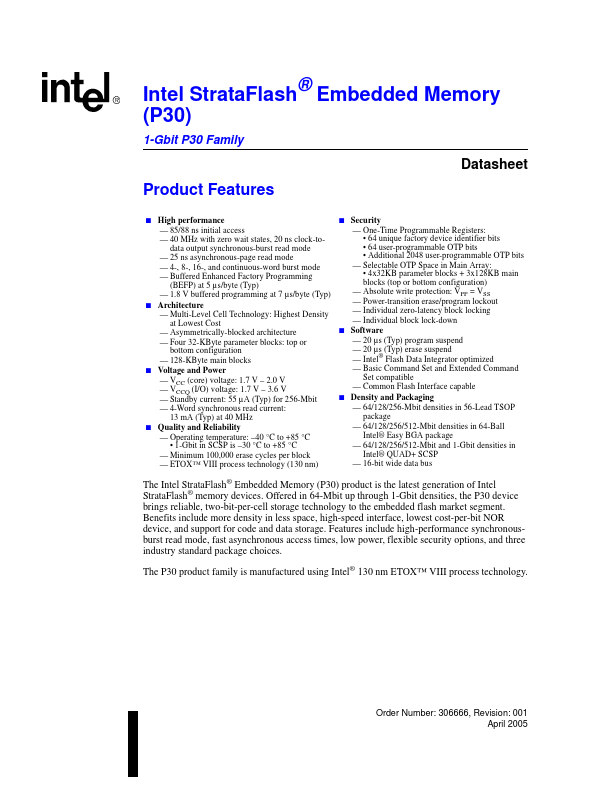

Key Features

- High performance

- 85/88 ns initial access

- One-Time Programmable Registers

- 40 MHz with zero wait states, 20 ns clock-todata output synchronous-burst read mode

- 64 unique factory device identifier bits