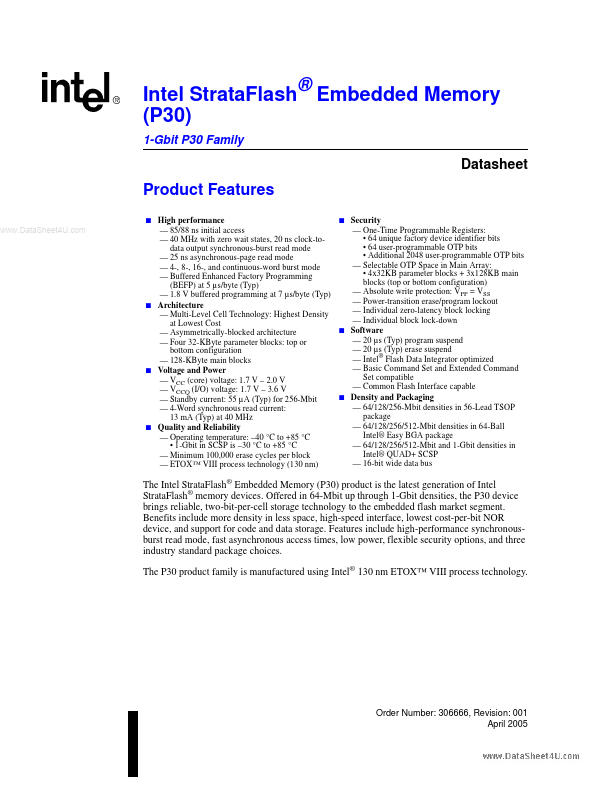

128P308 Overview

Key Features

- High performance

- 85/88 ns initial access

- One-Time Programmable Registers

- 64 unique factory device identifier bits

- 40 MHz with zero wait states, 20 ns clock-to

- 64 user-programmable OTP bits data output synchronous-burst read mode

- Additional 2048 user-programmable OTP bits

- 25 ns asynchronous-page read mode

- Selectable OTP Space in Main Array

- 4-, 8-, 16-, and continuous-word burst mode