IS61VPS25672A Key Features

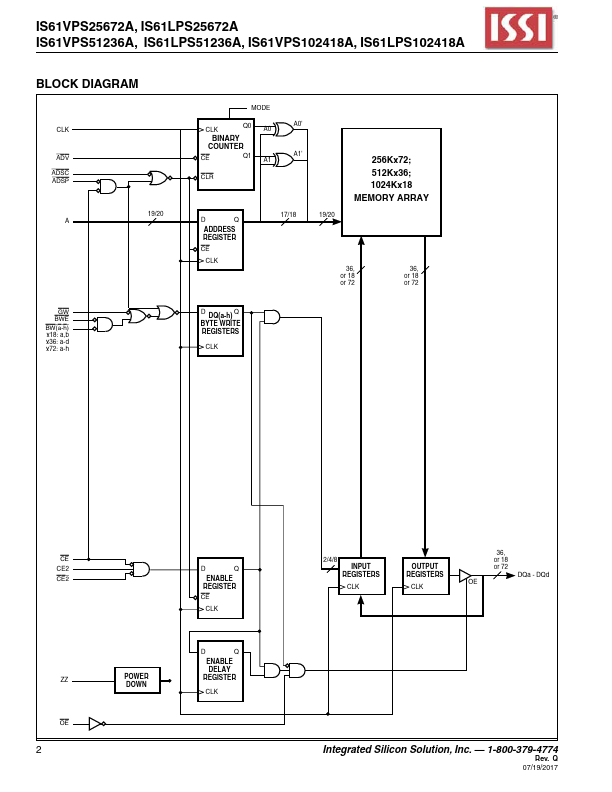

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and

- Burst sequence control using MODE input

- Three chip enable option for simple depth ex

- mon data inputs and data outputs

- Auto Power-down during deselect

- Single cycle deselect

- Snooze MODE for reduced-power standby

- JTAG Boundary Scan for PBGA package