IDTCV104B

Description

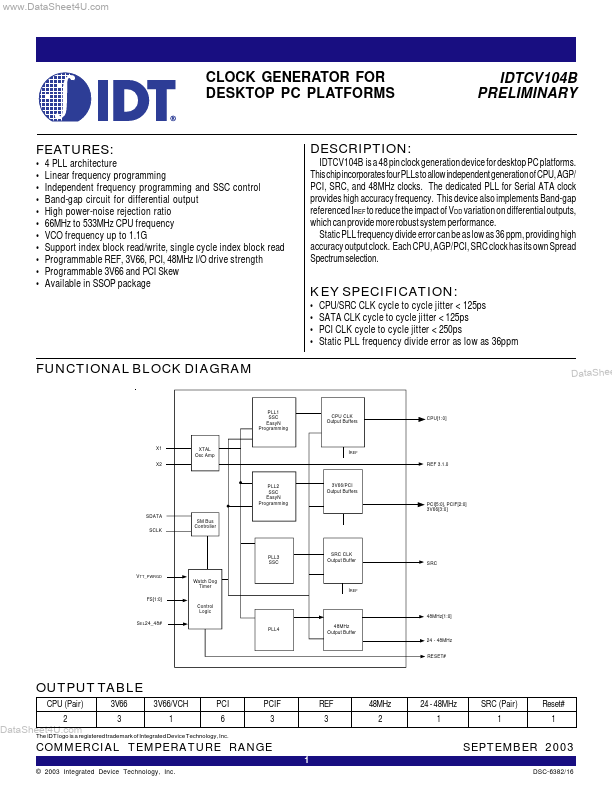

KEY SPECIFICATION: - - - - CPU/SRC CLK cycle to cycle jitter < 125ps SATA CLK cycle to cycle jitter < 125ps PCI CLK cycle to cycle jitter < 250ps Static PLL frequency divide error as low as 36ppm FUNCTIONAL.

Key Features

- This chip incorporates four PLLs to allow independent generation of CPU, AGP/ PCI, SRC, and 48MHz clocks

- The dedicated PLL for Serial ATA clock provides high accuracy frequency

- Static PLL frequency divide error can be as low as 36 ppm, providing high accuracy output clock

- Each CPU, AGP/PCI, SRC clock has its own Spread Spectrum selection