IDT74FCT543C

IDT74FCT543C is FAST CMOS OCTAL LATCHED TRANSCEIVER manufactured by Integrated Device Technology.

- Part of the IDT74FCT543 comparator family.

- Part of the IDT74FCT543 comparator family.

IDT54/74FCT543/A/C FAST CMOS OCTAL LATCHED TRANSCEIVER

FAST CMOS OCTAL LATCHED TRANSCEIVER

MILITARY AND MERCIAL TEMPERATURE RANGES

IDT54/74FCT543/A/C

Features

:

- IDT54FCT543 equivalent to FAST™ speed

- IDT54/74FCT543A up to 25% faster than FAST

- IDT74FCT543C up to 40% faster than FAST

- Eqivalent to FAST output drive over full temperature and voltage supply extremes

- IOL = 64m A (mercial) and 48m A (military)

- Separate controls for data flow in each direction

- Back-to-back latches for storage

- CMOS power levels (1m W typ. static)

- Substantially lower input current levels than FAST (5µA max.)

- TTL input and output level patible

- CMOS output level patible

- MIlitary product pliant to MIL-STD-883, Class B

- Available in the following packages:

- mercial: SOIC

- Military: CERDIP, LCC

DESCRIPTION:

The FCT543 is a non-inverting octal transceiver built using an advanced dual metal CMOS technology. These devices contain two sets of eight Dtype latches with separate input and output controls for each set. For data flow from A to B, for example, the A-to-B Enable (CEAB) input must be low in order to enter data from A0- A7 or to take data from B0- B7, as indicated in the Function Table. With CEAB low, a low signal on the A-to-B Latch Enable (LEAB) input makes the A-to-B latches transparent; a subsequent low-to-high transition of the LEAB signal puts the A latches in the storage mode and their outputs no longer change with the A inputs. With CEAB and OEAB both low, the 3-state B output buffers are active and reflect the data present at the output of the A latches. Control of data from B to A is similar, but uses the CEBA, LEBA and OEBA inputs.

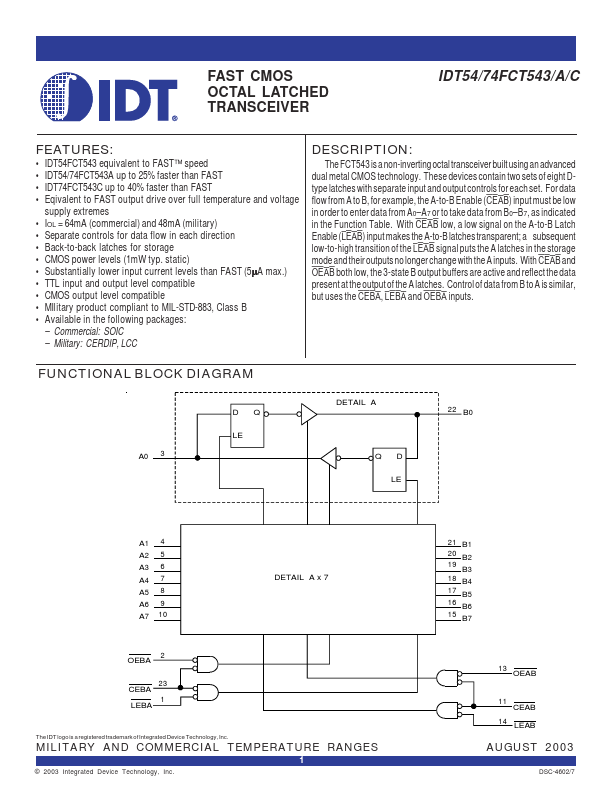

FUNCTIONAL BLOCK DIAGRAM

A0 3

DQ LE

DETAIL A

QD LE

22 B0

A1 4 A2 5 A3 6 A4 7 A5 8 A6 9 A7...