ICS874005-04 Overview

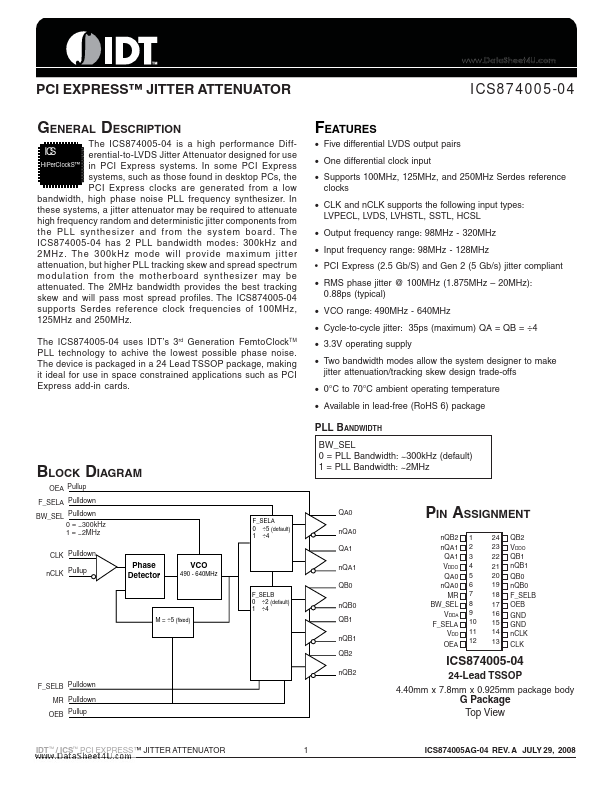

The ICS874005-04 is a high performance DiffIC S erential-to-LVDS Jitter Attenuator designed for use HiPerClockS™ in PCI Express systems. In some PCI Express systems, such as those found in desktop PCs, the PCI Express clocks are generated from a low bandwidth, high phase noise PLL frequency synthesizer. In these systems, a jitter attenuator may be required to attenuate high frequency random and deterministic jitter...

ICS874005-04 Key Features

- Five differential LVDS output pairs

- One differential clock input

- Supports 100MHz, 125MHz, and 250MHz Serdes reference clocks

- CLK and nCLK supports the following input types: LVPECL, LVDS, LVHSTL, SSTL, HCSL

- Output frequency range: 98MHz

- 320MHz

- Input frequency range: 98MHz

- 128MHz

- PCI Express (2.5 Gb/S) and Gen 2 (5 Gb/s) jitter pliant

- RMS phase jitter @ 100MHz (1.875MHz