IS61VPS12836EC Overview

Description

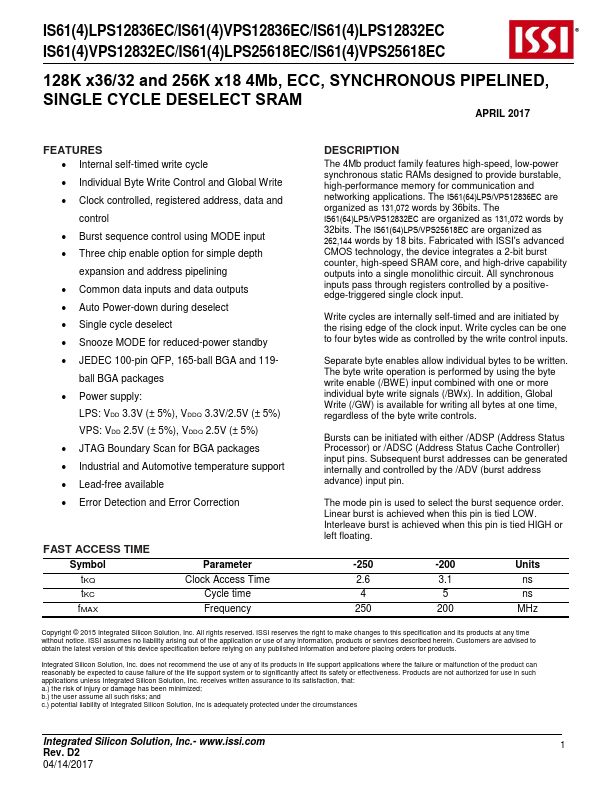

The 4Mb product family features high-speed, low-power synchronous static RAMs designed to provide burstable, high-performance memory for communication and networking applications. The IS61(64)LPS/VPS12836EC are organized as 131,072 words by 36bits.

Key Features

- Internal self-timed write cycle

- Individual Byte Write Control and Global Write

- Clock controlled, registered address, data and control

- Burst sequence control using MODE input

- Three chip enable option for simple depth expansion and address pipelining

- Common data inputs and data outputs

- Auto Power-down during deselect

- Single cycle deselect

- Snooze MODE for reduced-power standby

- JEDEC 100-pin QFP, 165-ball BGA and 119- ball BGA packages