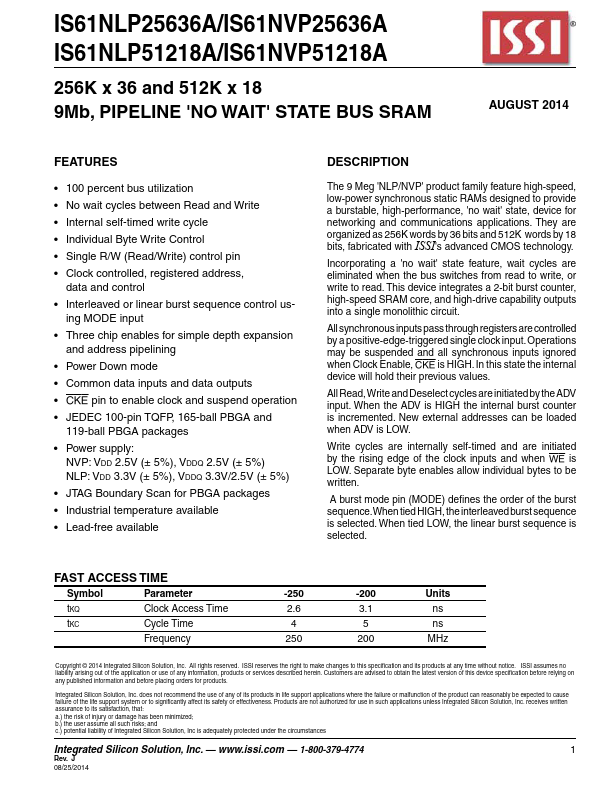

IS61NVP51218A

Overview

The 9 Meg 'NLP/NVP' product family feature high-speed, low-power synchronous static RAMs designed to provide a burstable, high-performance, 'no wait' state, device for networking and communications applications. They are organized as 256K words by 36 bits and 512K words by 18 bits, fabricated with ISSI's advanced CMOS technology.

- 100 percent bus utilization

- No wait cycles between Read and Write

- Internal self-timed write cycle

- Individual Byte Write Control

- Single R/W (Read/Write) control pin

- Clock controlled, registered address, data and control

- Interleaved or linear burst sequence control us- ing MODE input

- Three chip enables for simple depth expansion and address pipelining

- Power Down mode

- Common data inputs and data outputs