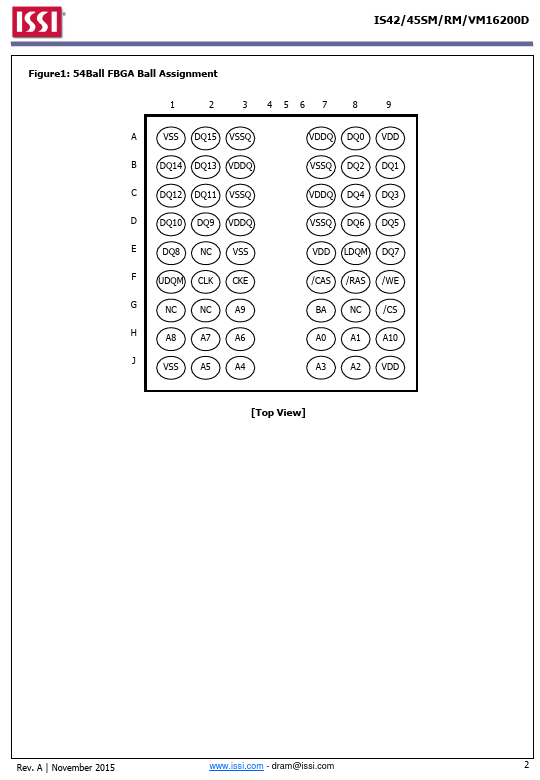

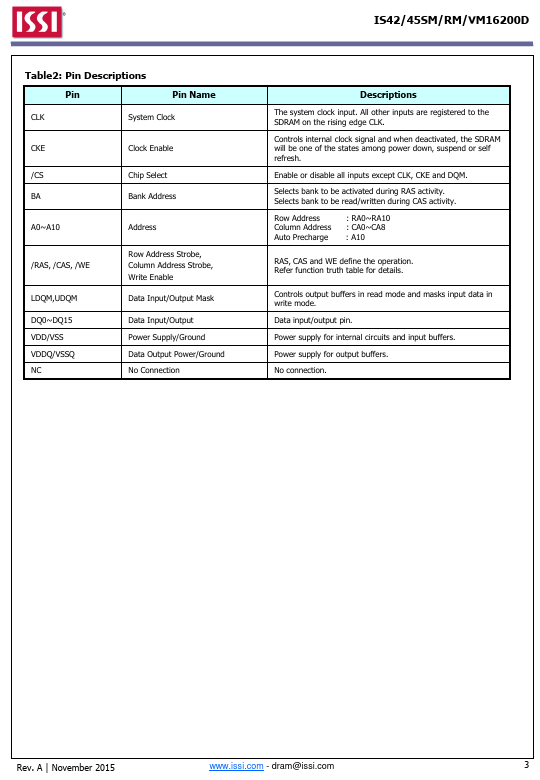

Datasheet Summary

IS42/45SM/RM/VM16200D

1M x 16Bits x 2Banks Low Power Synchronous DRAM

Description

These IS42SM/RM/VM16200D are low power 33,554,432 bits CMOS Synchronous DRAM organized as 2 banks of 1,048,576 words x 16 bits. These products are offering fully synchronous operation and are referenced to a positive edge of the clock. All inputs and outputs are synchronized with the rising edge of the clock input. The data paths are internally pipelined to achieve high bandwidth. All input and output voltage levels are patible with LVCMOS.

Features

- JEDEC standard 3.3V, 2.5V, 1.8V power supply

- Auto refresh and self refresh

- All pins are patible with LVCMOS interface

- 4K refresh cycle / 64ms

-...