IDT71V3557SA Datasheet Text

128K x 36, 256K x 18, 3.3V Synchronous ZBT™ SRAMs 3.3V I/O, Burst Counter, Flow-Through Outputs

IDT71V3557S IDT71V3559S IDT71V3557SA IDT71V3559SA

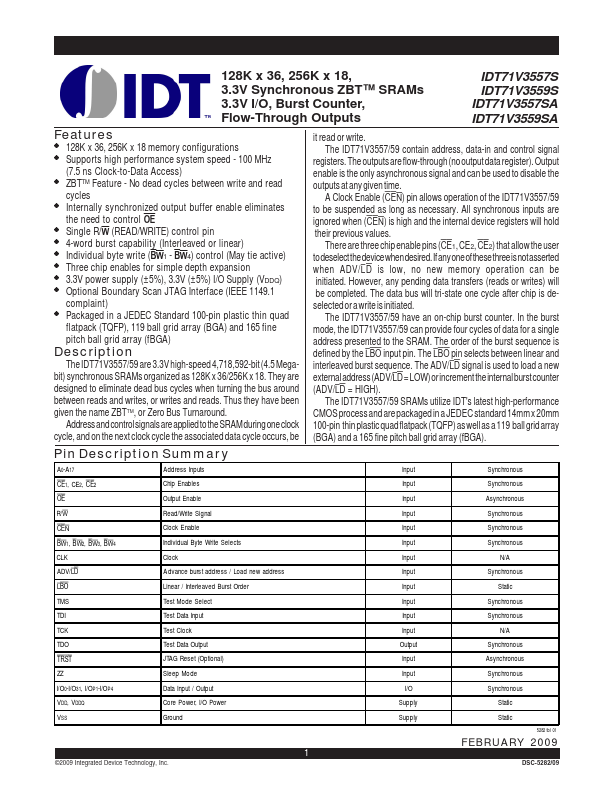

Features

- 128K x 36, 256K x 18 memory configurations

- Supports high performance system speed

- 100 MHz

(7.5 ns Clock-to-Data Access)

- ZBTTM Feature

- No dead cycles between write and read cycles

- Internally synchronized output buffer enable eliminates the need to control OE

- Single R/W (READ/WRITE) control pin

- 4-word burst capability (Interleaved or linear)

- Individual byte write (BW1

- BW4) control (May tie active)

- Three chip enables for simple depth expansion

- 3.3V power supply (±5%), 3.3V (±5%) I/O Supply (VDDQ)

- Optional Boundary Scan JTAG Interface (IEEE 1149.1 plaint)

- Packaged in a JEDEC Standard 100-pin plastic thin quad flatpack (TQFP), 119 ball grid array (BGA) and 165 fine pitch ball grid array (fBGA)

Description

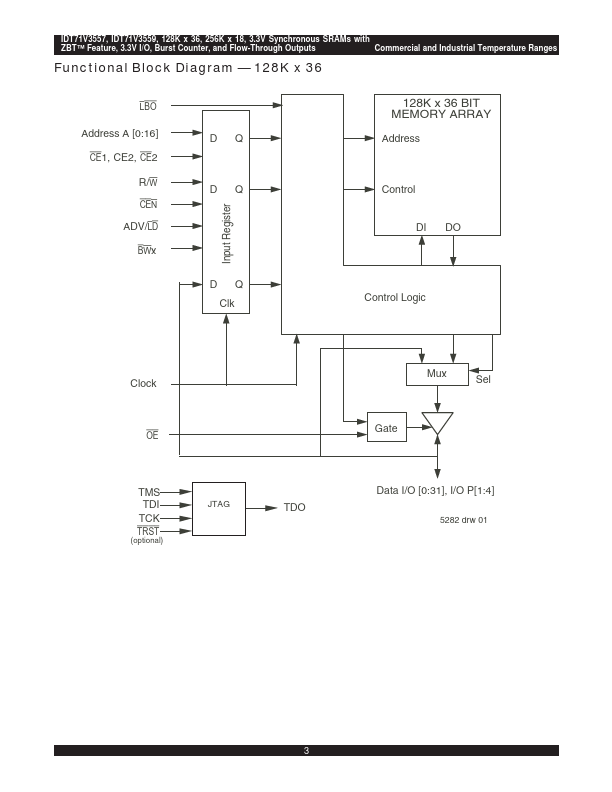

The IDT71V3557/59 are 3.3V high-speed 4,718,592-bit (4.5 Megabit)...