IDT71P72204

Overview

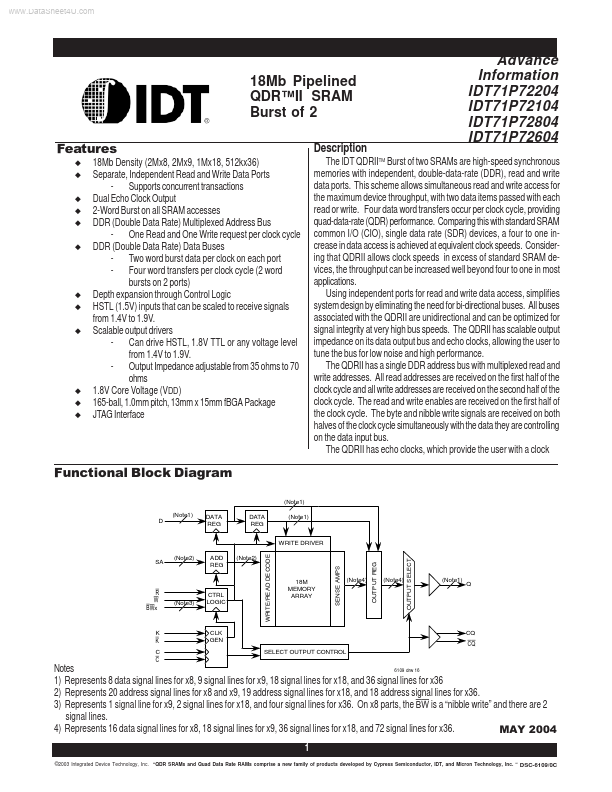

Advance Information IDT71P72204 IDT71P72104 IDT71P72804 IDT71P72604 x x x x x x 18Mb Density (2Mx8, 2Mx9, 1Mx18, 512kx36) Separate, Independent Read and Write Data Ports Supports concurrent transactions Dual Echo Clock Output 2-Word Burst on all SRAM accesses DDR (Double Data Rate) Multiplexed Address Bus One Read and One Write request per clock cycle DDR (Double Data Rate) Data Buses Two word burst data per clock on each port Four word transfers per clock cycle (2 word bursts on 2 ports) Depth expansion through Control Logic HSTL (1.5V) inputs that can be scaled to receive signals from 1.4V to 1.9V. Scalable output drivers Can drive HSTL, 1.8V TTL or any voltage level from 1.4V to 1.9V.