ICS673-01 Description

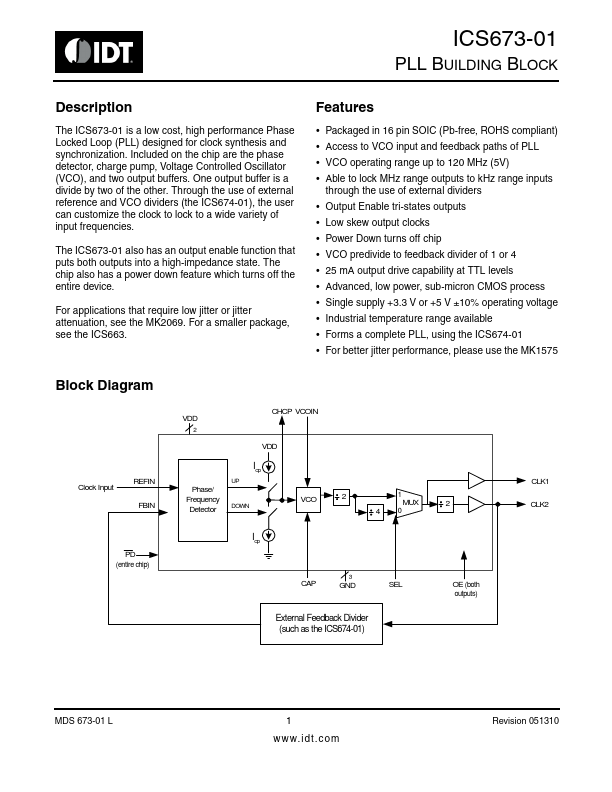

The ICS673-01 is a low cost, high performance Phase Locked Loop (PLL) designed for clock synthesis and synchronization. Included on the chip are the phase detector, charge pump, Voltage Controlled Oscillator (VCO), and two output buffers. One output buffer is a divide by two of the other.

ICS673-01 Key Features

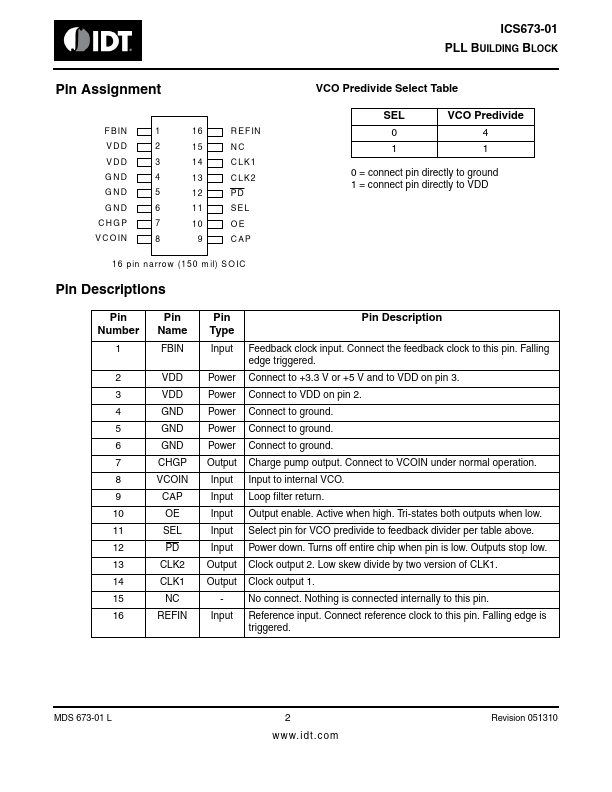

- Packaged in 16 pin SOIC (Pb-free, ROHS pliant)

- Access to VCO input and feedback paths of PLL

- VCO operating range up to 120 MHz (5V)

- Able to lock MHz range outputs to kHz range inputs

- Output Enable tri-states outputs

- Low skew output clocks

- Power Down turns off chip

- VCO predivide to feedback divider of 1 or 4

- 25 mA output drive capability at TTL levels

- Advanced, low power, sub-micron CMOS process

ICS673-01 Applications

- Packaged in 16 pin SOIC (Pb-free, ROHS pliant)

- Access to VCO input and feedback paths of PLL

- VCO operating range up to 120 MHz (5V)

- Able to lock MHz range outputs to kHz range inputs