8SLVS1118

8SLVS1118 is Low Additive Jitter LVDS/ LVPECL Fanout Buffer manufactured by IDT.

Description

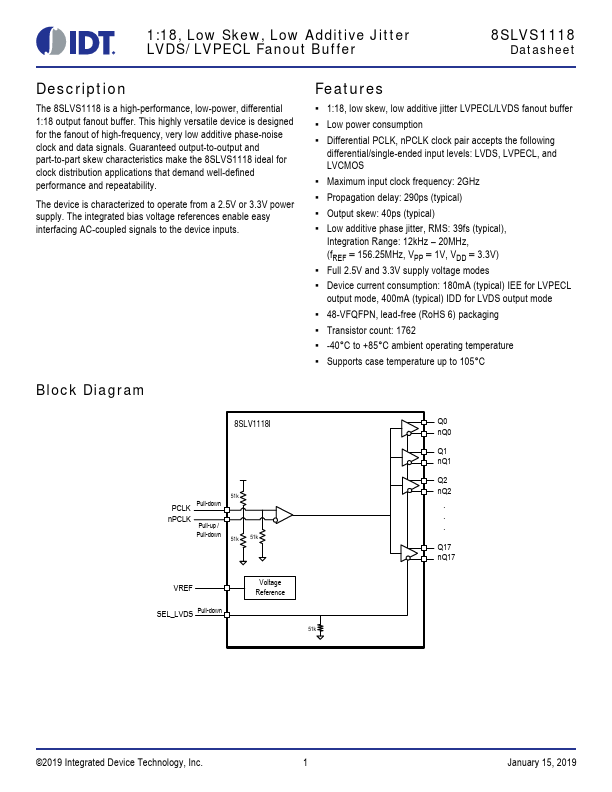

The 8SLVS1118 is a high-performance, low-power, differential 1:18 output fanout buffer. This highly versatile device is designed for the fanout of high-frequency, very low additive phase-noise clock and data signals. Guaranteed output-to-output and part-to-part skew characteristics make the 8SLVS1118 ideal for clock distribution applications that demand well-defined performance and repeatability.

The device is characterized to operate from a 2.5V or 3.3V power supply. The integrated bias voltage references enable easy interfacing AC-coupled signals to the device inputs.

Features

- 1:18, low skew, low additive jitter LVPECL/LVDS fanout buffer

- Low power consumption

- Differential PCLK, n PCLK clock pair accepts the following differential/single-ended input levels: LVDS, LVPECL, and LVCMOS

- Maximum input clock frequency: 2GHz

- Propagation delay: 290ps (typical)

- Output skew:...