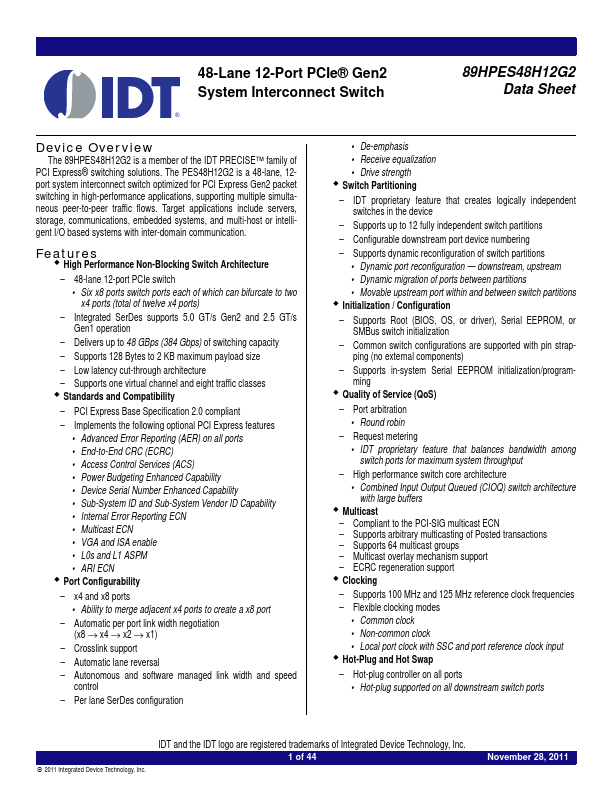

89HPES48H12G2

Overview

The 89HPES48H12G2 is a member of the IDT PRECISE™ family of PCI Express® switching solutions. The PES48H12G2 is a 48-lane, 12port system interconnect switch optimized for PCI Express Gen2 packet switching in high-performance applications, supporting multiple simultaneous peer-to-peer traffic flows. Target applications include servers, storage, munications, embedded systems, and multi-host or intelligent I/O based systems with inter-domain munication.

Features

- High Performance Non-Blocking Switch Architecture

- 48-lane 12-port PCIe switch

- Six x8 ports switch ports each of which can bifurcate to two x4 ports (total of twelve x4 ports)

- Integrated Ser Des supports 5.0 GT/s Gen2 and 2.5 GT/s Gen1 operation

- Delivers up to 48 GBps (384 Gbps) of switching capacity

- Supports 128 Bytes to 2 KB maximum payload size

- Low latency cut-through architecture

-...