87002-02 Key Features

- Two LVCMOS/LVTTL outputs, 7 typical output impedance

- CLK, nCLK pair can accept the following differential

- Internal bias on nCLK to support LVCMOS/LVTTL levels on CLK

- Output frequency range: 15.625MHz to 250MHz

- Input frequency range: 15.625MHz to 250MHz

- VCO range: 250MHz to 500MHz

- External feedback for “zero delay” clock regeneration

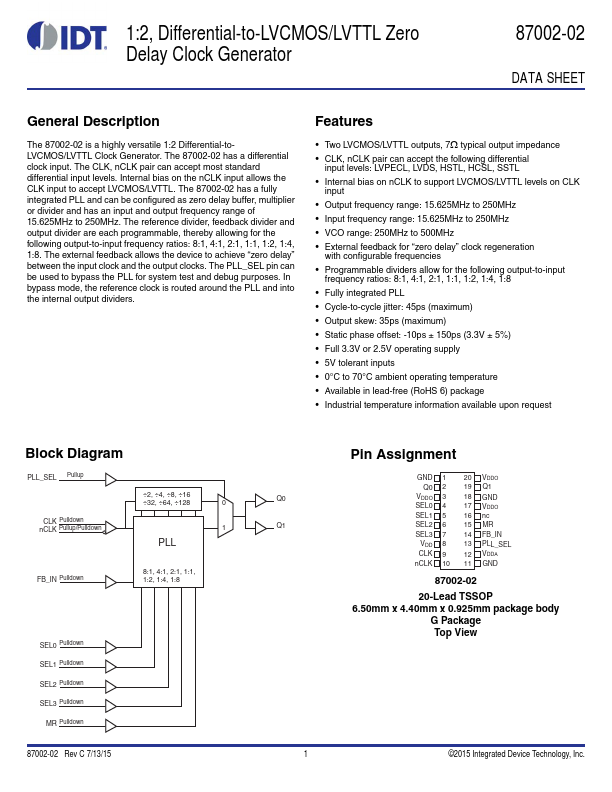

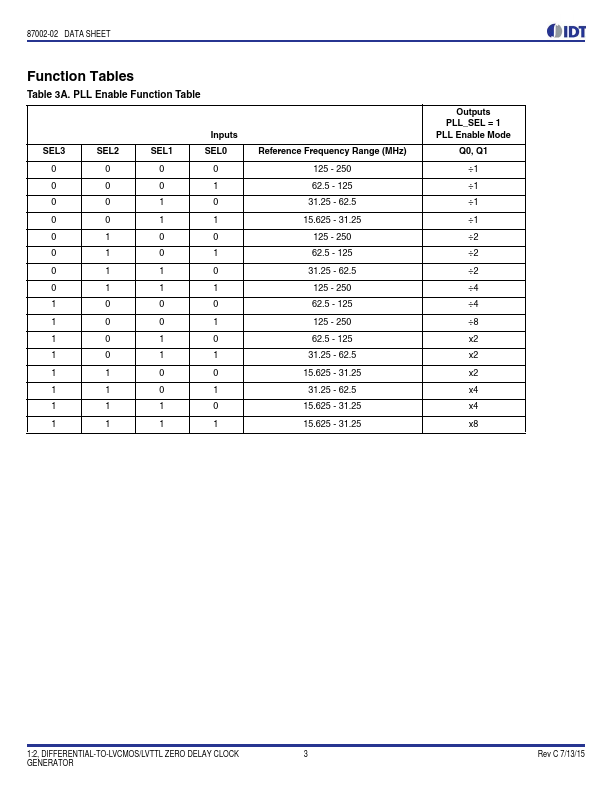

- Programmable dividers allow for the following output-to-input

- Fully integrated PLL

- Cycle-to-cycle jitter: 45ps (maximum)