524S

Description

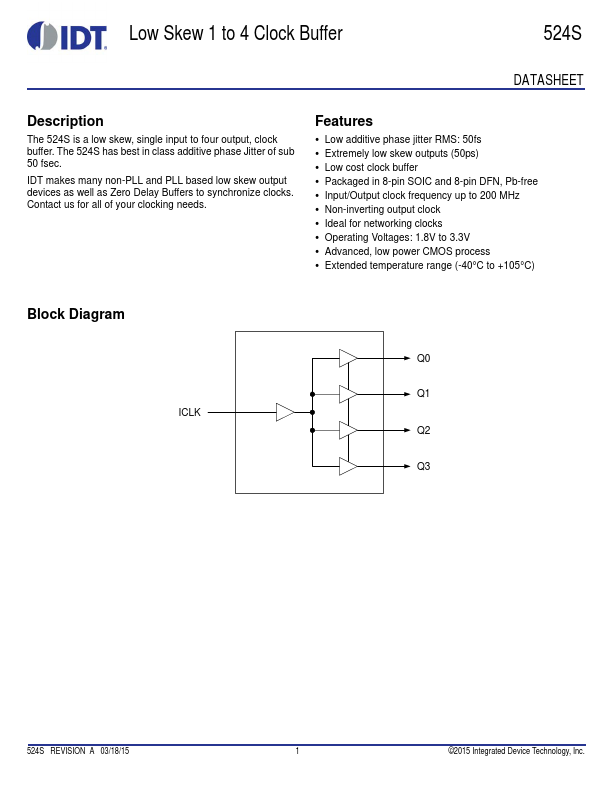

The 524S is a low skew, single input to four output, clock buffer. The 524S has best in class additive phase Jitter of sub 50 fsec.

Key Features

- Low additive phase jitter RMS: 50fs

- Extremely low skew outputs (50ps)

- Low cost clock buffer

- Packaged in 8-pin SOIC and 8-pin DFN, Pb-free

- Input/Output clock frequency up to 200 MHz

- Non-inverting output clock

- Ideal for networking clocks

- Operating Voltages: 1.8V to 3.3V

- Advanced, low power CMOS process

- Extended temperature range (-40°C to +105°C)