ICS548-03 Overview

Description

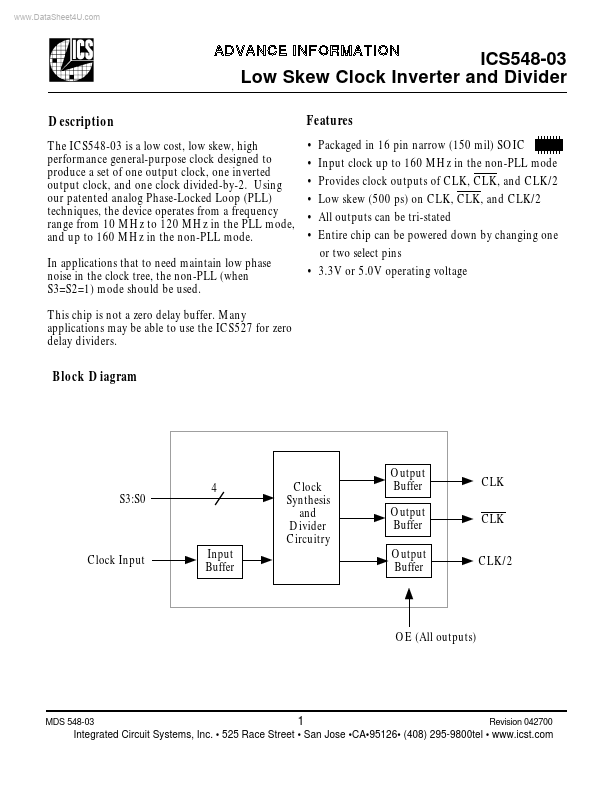

The ICS548-03 is a low cost, low skew, high performance general-purpose clock designed to produce a set of one output clock, one inverted output clock, and one clock divided-by-2. Using our patented analog Phase-Locked Loop (PLL) techniques, the device operates from a frequency range from 10 MHz to 120 MHz in the PLL mode, and up to 160 MHz in the non-PLL mode.

Key Features

- 3.3V or 5.0V operating voltage