| Part | HYMP112U64CR8-S6 |

|---|---|

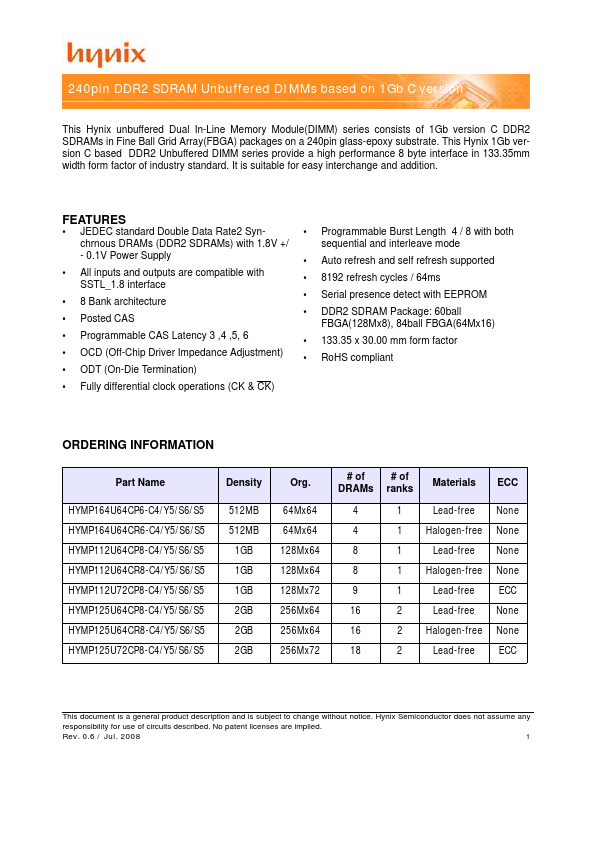

| Description | 240pin DDR2 SDRAM Unbuffered DIMMs based on 1Gb C version |

| Manufacturer | SK Hynix |

| Size | 252.14 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| Q-67106-H6514 | Siemens Semiconductor Group | PLL-Frequency Synthesizer PMB2306R/PMB2306T Version 2.2 |

| S50K | International Rectifier | FAST RECOVERY DIODES Hockey Puk Version |

| SD1053C | International Rectifier | FAST RECOVERY DIODES Hockey Puk Version |