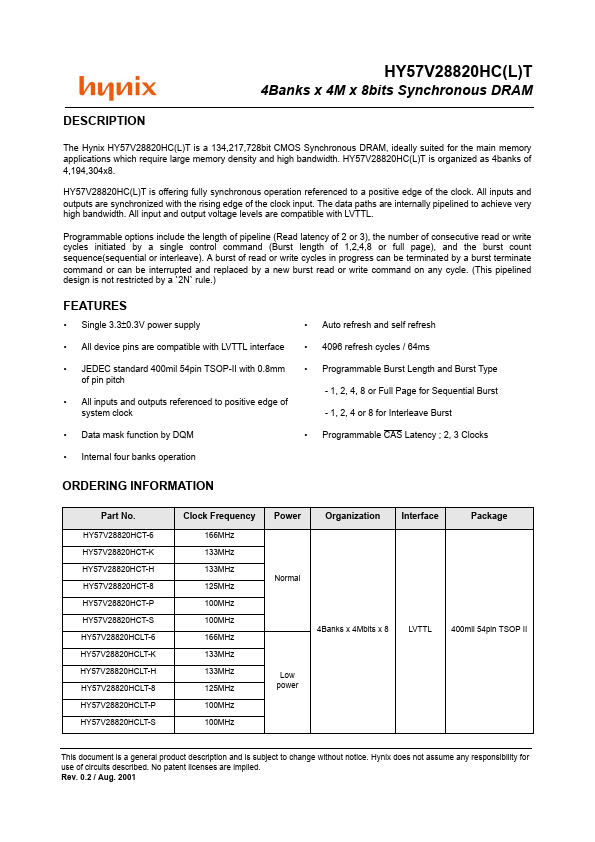

HY57V28820HCLT Description

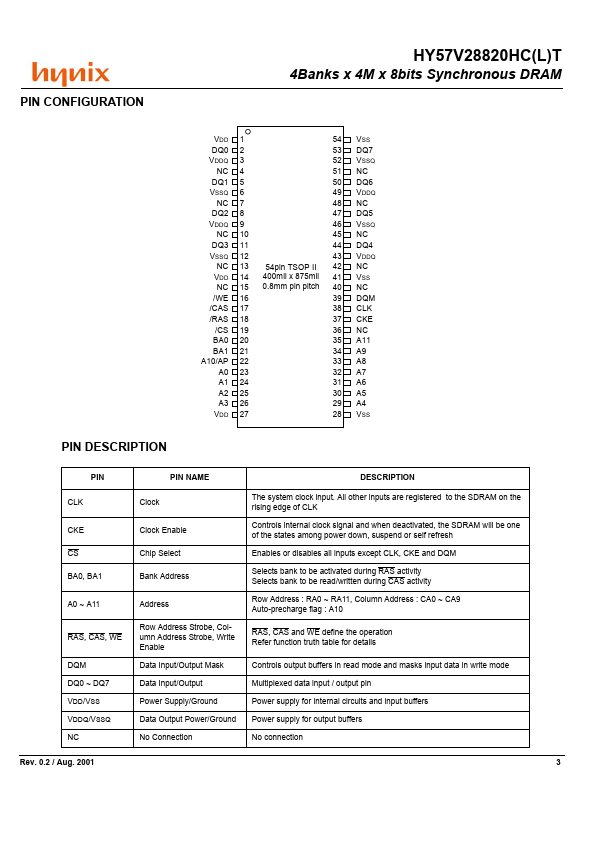

The Hynix HY57V28820HC(L)T is a 134,217,728bit CMOS Synchronous DRAM, ideally suited for the main memory applications which require large memory density and high bandwidth. HY57V28820HC(L)T is organized as 4banks of 4,194,304x8. HY57V28820HC(L)T is offering fully synchronous operation referenced to a positive edge of the clock.