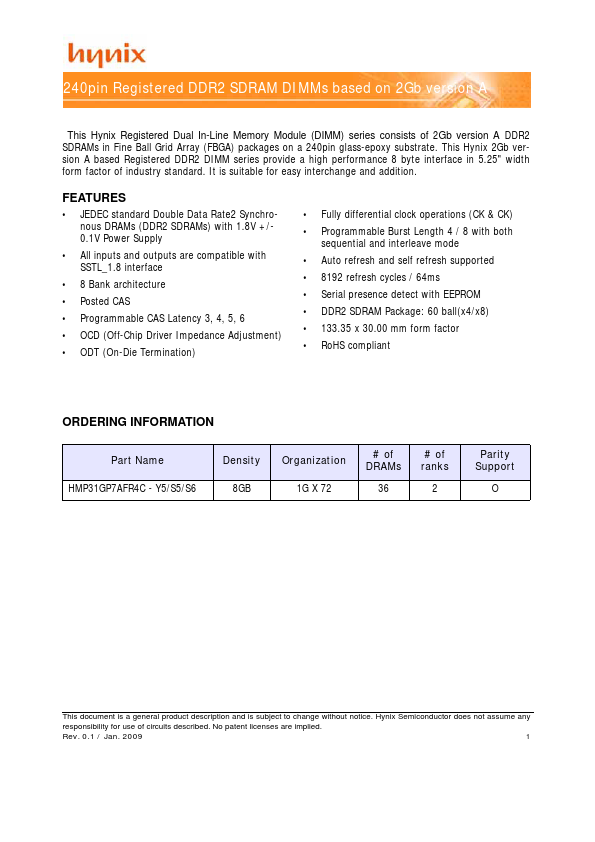

HMP31GP7AFR4C-Y5

Key Features

- JEDEC standard Double Data Rate2 Synchronous DRAMs (DDR2 SDRAMs) with 1.8V +/0.1V Power Supply All inputs and outputs are compatible with SSTL_1.8 interface 8 Bank architecture Posted CAS Programmable CAS Latency 3, 4, 5, 6 OCD (Off-Chip Driver Impedance Adjustment) ODT (On-Die Termination) * * * * * * *

- Fully differential clock operations (CK & CK) Programmable Burst Length 4 / 8 with both sequential and interleave mode Auto refresh and self refresh supported 8192 refresh cycles / 64ms Serial presence detect with EEPROM DDR2 SDRAM Package: 60 ball(x4/x8) 133.35 x 30.00 mm form factor RoHS compliant * * * * *