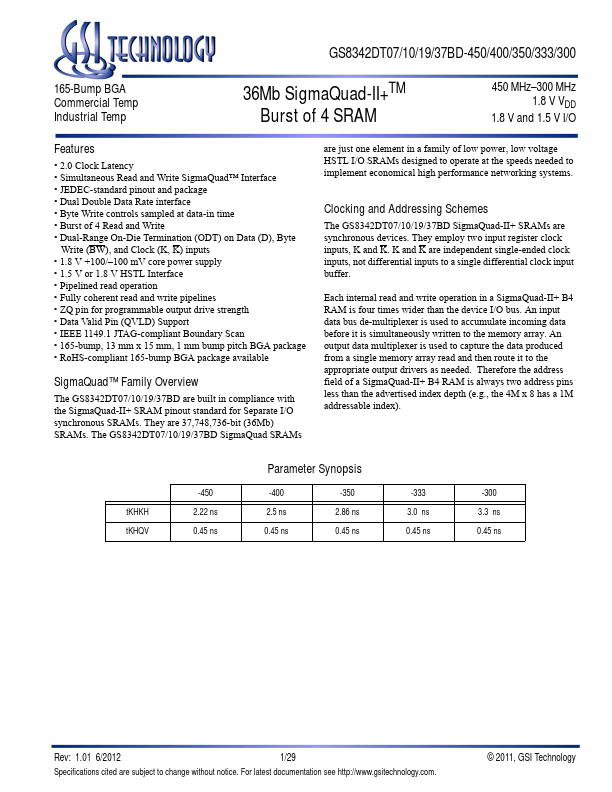

GS8342DT19BD

Overview

- 2.0 Clock Latency

- Simultaneous Read and Write SigmaQuad™ Interface

- JEDEC-standard pinout and package

- Dual Double Data Rate interface

- Byte Write controls sampled at data-in time

- Burst of 4 Read and Write

- Dual-Range On-Die Termination (ODT) on Data (D), Byte Write (BW), and Clock (K, K) inputs

- 1.8 V +100/-100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation