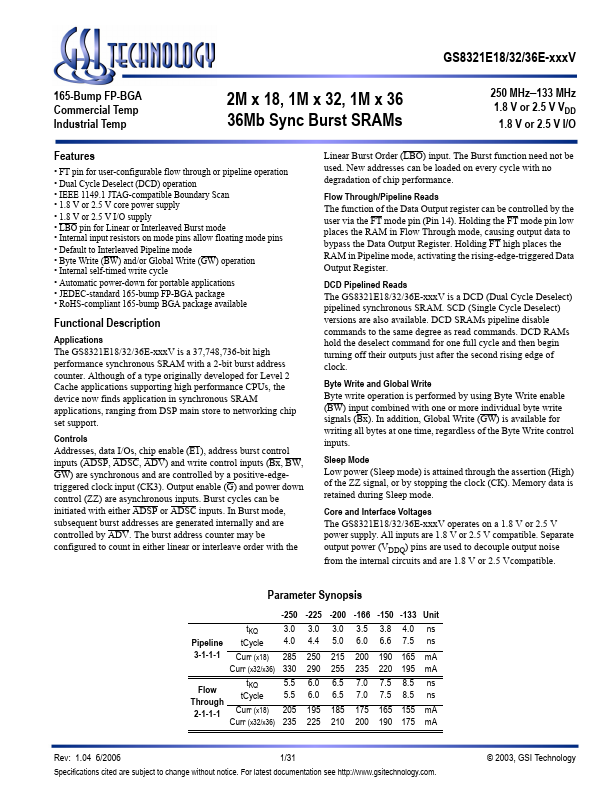

| Part | GS8321E18E-V |

|---|---|

| Description | 36Mb Sync Burst SRAMs |

| Manufacturer | GSI Technology |

| Size | 724.12 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| N04L1630C2B | AMI SEMICONDUCTOR | 4Mb Ultra-Low Power Asynchronous CMOS SRAMs |

| N25S830HA | onsemi | 256 kb Low Power Serial SRAMs |

| N01L083WC2A | NanoAmp Solutions | Ultra-low Power SRAMs |