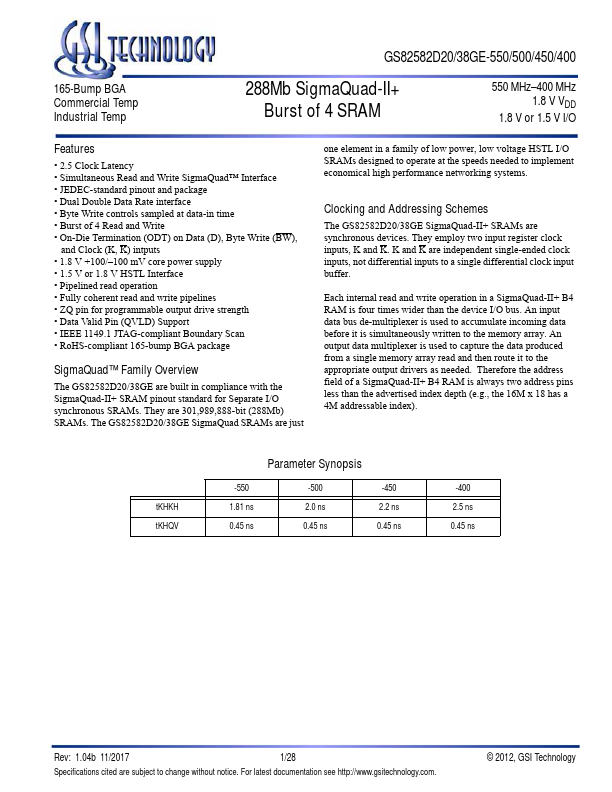

GS82582D38GE Overview

Key Specifications

Operating Voltage: 1.8 V

Max Voltage (typical range): 1.9 V

Min Voltage (typical range): 1.7 V

Length: 17 mm

Key Features

- 2.5 Clock Latency

- Simultaneous Read and Write SigmaQuad™ Interface

- JEDEC-standard pinout and package

- Dual Double Data Rate interface

- Burst of 4 Read and Write