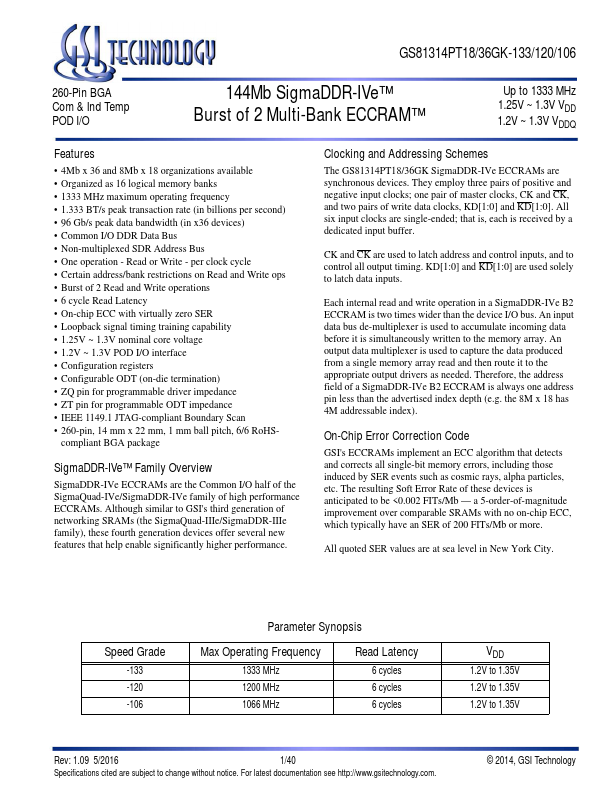

GS81314PT18GK Overview

Key Features

- 4Mb x 36 and 8Mb x 18 organizations available

- Organized as 16 logical memory banks

- 1333 MHz maximum operating frequency

- 1.333 BT/s peak transaction rate (in billions per second)

- 96 Gb/s peak data bandwidth (in x36 devices)

- Common I/O DDR Data Bus

- Non-multiplexed SDR Address Bus

- One operation

- Read or Write

- per clock cycle