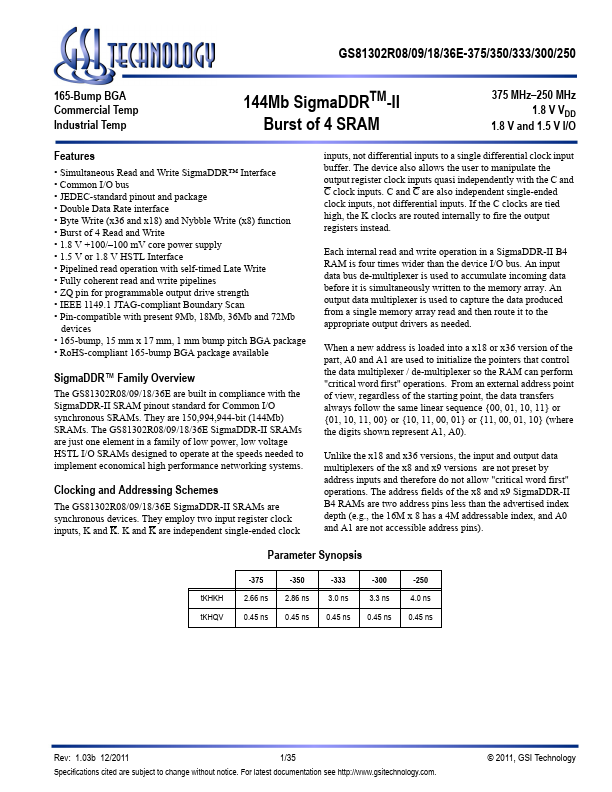

GS81302R36E

Overview

- Simultaneous Read and Write SigmaDDR™ Interface

- Common I/O bus

- JEDEC-standard pinout and package

- Double Data Rate interface

- Byte Write (x36 and x18) and Nybble Write (x8) function

- Burst of 4 Read and Write

- 1.8 V +100/-100 mV core power supply

- 1.5 V or 1.8 V HSTL Interface

- Pipelined read operation with self-timed Late Write

- Fully coherent read and write pipelines