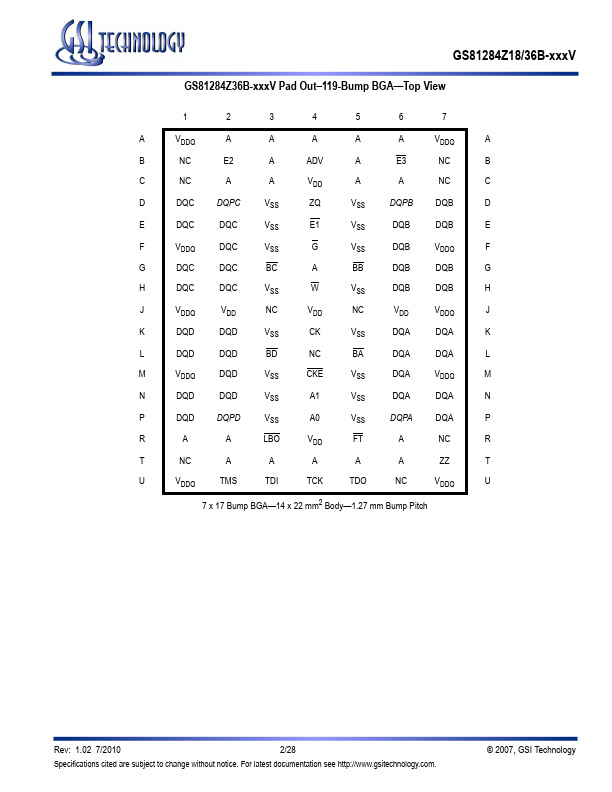

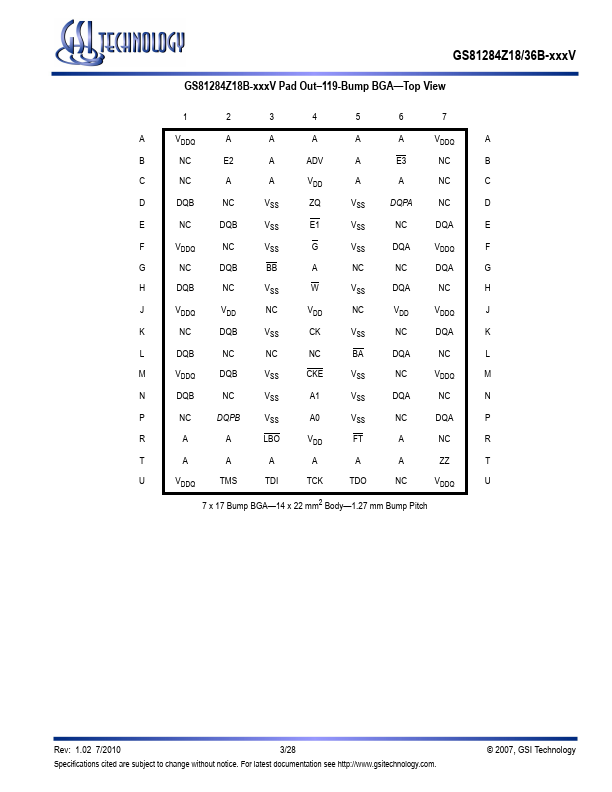

GS81284Z18B-xxxV Description

The GS81284Z18/36(B)-xxxV is a 144Mbit Synchronous Static SRAM.

GS81284Z18B-xxxV Key Features

- NBT (No Bus Turn Around) functionality allows zero wait Read-Write-Read bus utilization; fully pin-patible with both pip

- 1.8 V 2.5 V core power supply

- 1.8 V or 2.5 V I/O supply

- User-configurable Pipeline and Flow Through mode

- ZQ mode pin for user-selectable high/low output drive

- IEEE 1149.1 JTAG-patible Boundary Scan

- LBO pin for Linear or Interleave Burst mode

- Pin-patible with 8Mb, 36Mb, and 72Mb devices

- Byte write operation (9-bit Bytes)

- 3 chip enable signals for easy depth expansion