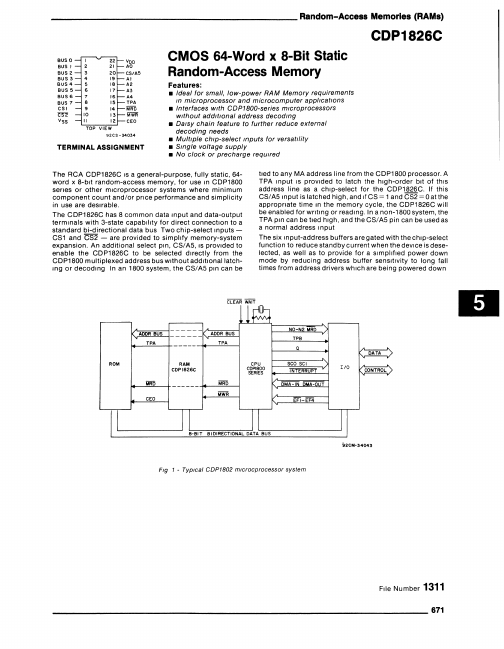

CDP1826C Overview

Key Specifications

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 6.5 V

Min Voltage (typical range): 4 V

Key Features

- Ideal for small, low-power RAM Memory requirements In microprocessor and microcomputer applications

- Interfaces with CDP1BOO-series microprocessors without additional address decoding

- DaiSY chain feature to further reduce external decoding needs

- Multiple chip-select Inputs for versatility

- Single voltage supply