DSP56002

features

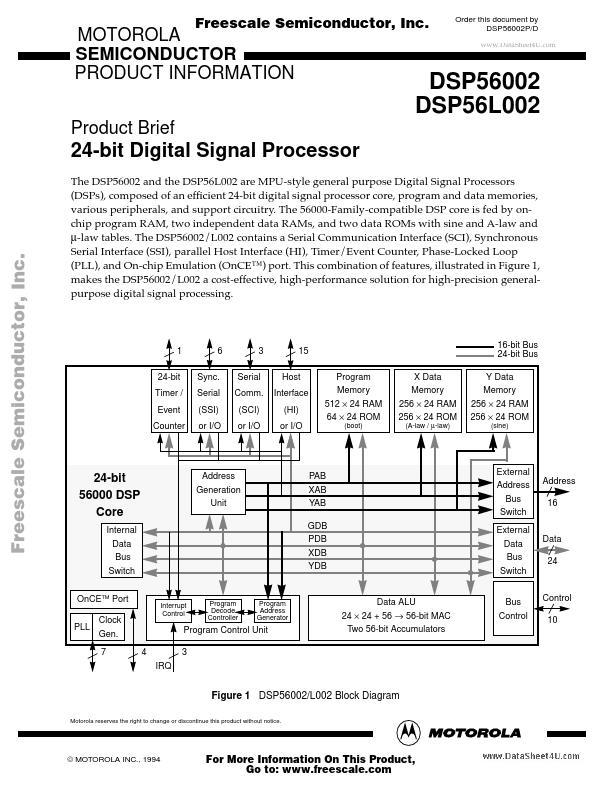

, illustrated in Figure 1, makes the DSP56002/L002 a cost-effective, high-performance solution for high-precision generalpurpose digital signal processing.

Freescale Semiconductor, Inc...

1 24-bit Timer / Event Counter

6 Sync. Serial (SSI) or I/O

3 Serial m. (SCI) or I/O

15 Host Interface (HI) or I/O Program Memory 512 × 24 RAM 64 × 24 ROM

(boot)

16-bit Bus 24-bit Bus X Data Memory 256 × 24 RAM 256 × 24 ROM

(A-law / µ-law)

Y Data Memory 256 × 24 RAM 256 × 24 ROM

(sine)

24-bit 56000 DSP Core

Internal Data Bus Switch On CETM Port PLL Clock Gen. 7 4 IRQ

Address Generation Unit

PAB XAB YAB GDB PDB XDB YDB

External Address Bus Switch External Data Bus Switch

Address 16

Data 24

Interrupt Control

Program Decode Controller

Program Address Generator

Program Control Unit 3

Data ALU 24 × 24 + 56 → 56-bit MAC Two 56-bit Accumulators

Bus Control

Control 10

Figure 1 DSP56002/L002 Block Diagram

Motorola reserves the right to change or discontinue this product without...