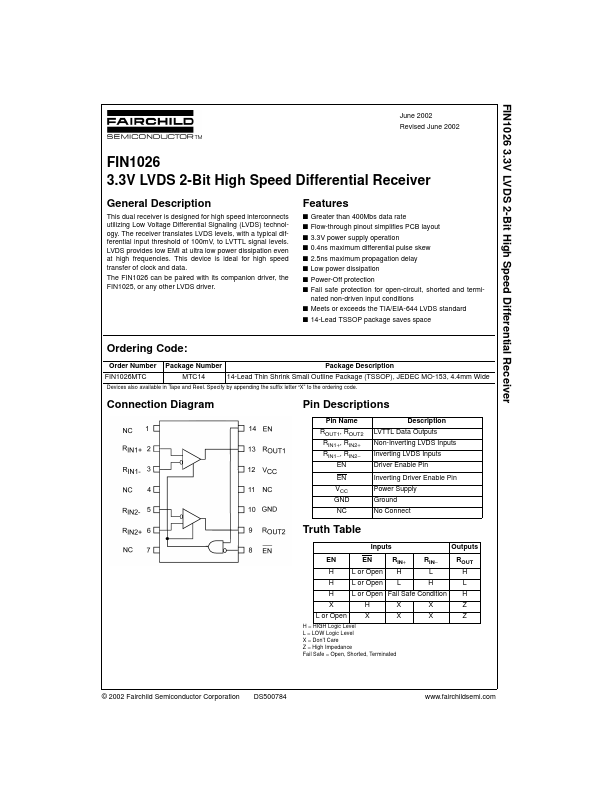

- Part: FIN1026

- Description: 3.3V LVDS 2-Bit High Speed Differential Receiver

- Manufacturer: Fairchild Semiconductor

- Size: 226.19 KB

Datasheets by Manufacturer

- VS838 — LFN — Infrared Receiver

- QN8075 — Quintic — Single-Chip Low-Power FM Receiver

- Si4825-A10 — Silicon Labs — BROADCAST MECHANICAL TUNING AM/FM/SW RADIO RECEIVER