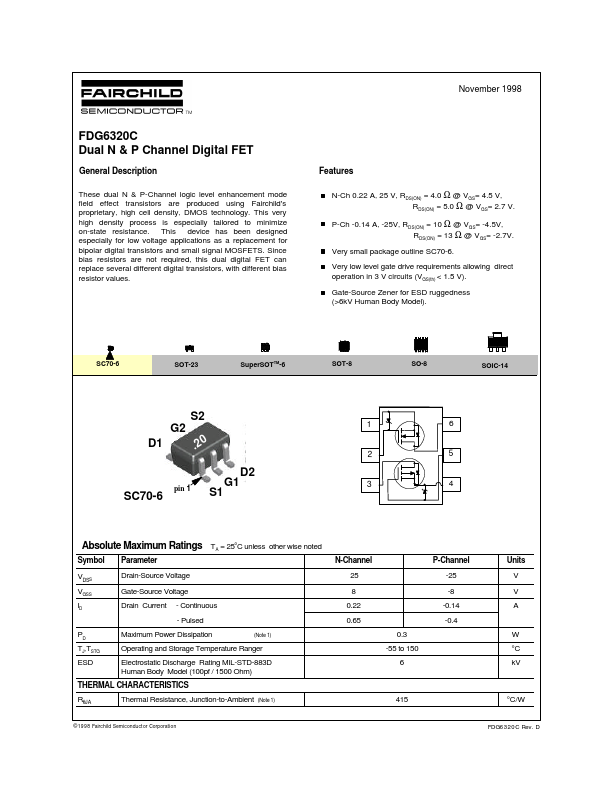

FDG6320C

Description

These dual N & P-Channel logic level enhancement mode field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance. This device has been designed especially for low voltage applications as a replacement for bipolar digital transistors and small signal MOSFETS. Since bias resistors are not required, this dual digital FET can replace several different digital transistors, with different bias resistor values.

Features

N-Ch 0.22 A, 25 V, RDS(ON) = 4.0 Ω @ VGS= 4.5 V, RDS(ON) = 5.0 Ω @ VGS= 2.7 V. P-Ch -0.14 A, -25V, RDS(ON) = 10 Ω @ VGS= -4.5V, RDS(ON) = 13 Ω @ VGS= -2.7V. Very small package outline SC70-6. Very low level gate drive requirements allowing direct operation in 3 V circuits (VGS(th) < 1.5 V). Gate-Source Zener for ESD ruggedness (>6k V Human Body Model).

SC70-6

SOT-23

Super SOTTM-6

SOT-8

SO-8

SOIC-14

S2 G2 D1

.20

G1...