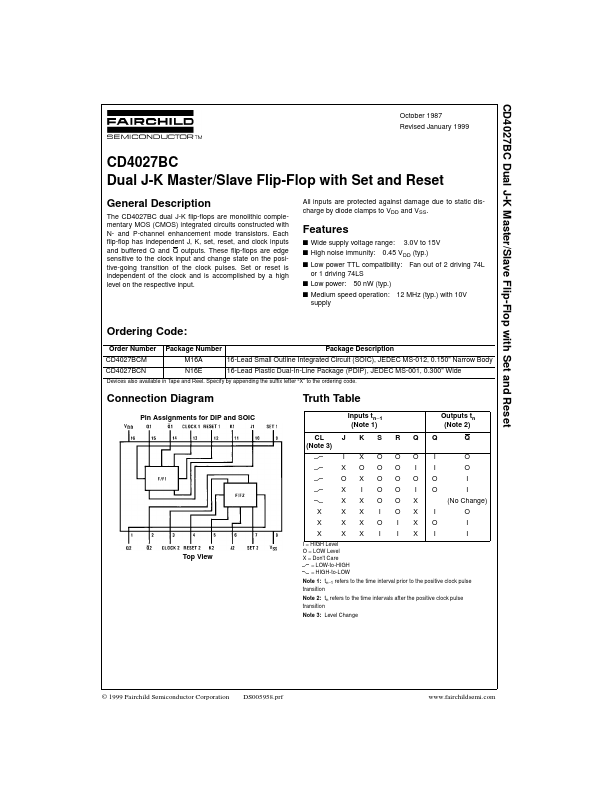

- Part: CD4027BCM

- Description: Dual J-K Master/Slave Flip-Flop

- Manufacturer: Fairchild Semiconductor

- Size: 56.43 KB

Other CD4027BCM Datasheets

| Manufacturer | Part Number | Description |

|---|---|---|

| CD4027BC | Dual J-K Master/Slave Flip-Flop | |

RCA

RCA |

CD4027B | CMOS DUAL J-K MASTER-SLAVER FLIP-FLOP |

Texas Instruments

Texas Instruments |

CD4027B | CMOS DUAL J-K MASTER-SLAVER FLIP-FLOP |

Texas Instruments

Texas Instruments |

CD4027BE | CMOS DUAL J-K MASTER-SLAVER FLIP-FLOP |

Texas Instruments

Texas Instruments |

CD4027BF | CMOS DUAL J-K MASTER-SLAVER FLIP-FLOP |