74LVQ00

Description

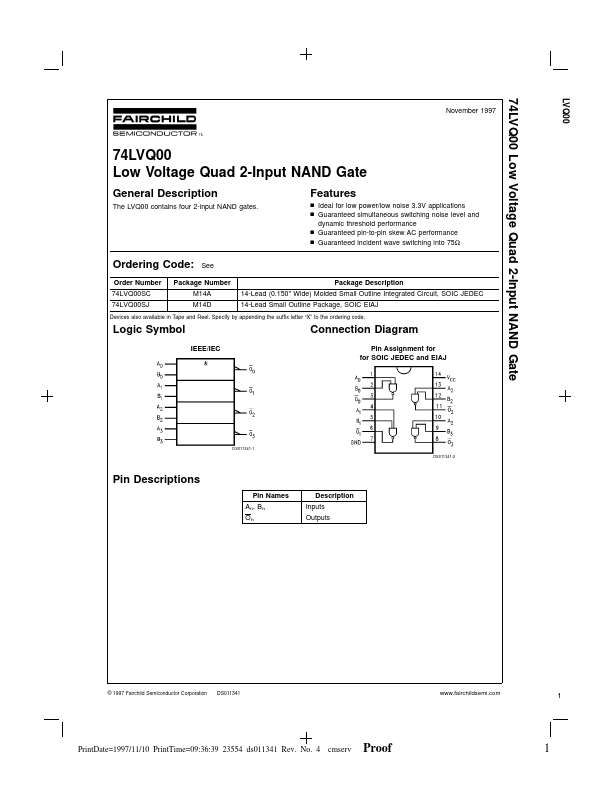

The LVQ00 contains four 2-input NAND gates.

Key Features

- n Ideal for low power/low noise 3.3V applications

- Guaranteed simultaneous switching noise level and dynamic threshold performance

- Guaranteed pin-to-pin skew AC performance

- Guaranteed incident wave switching into 75Ω