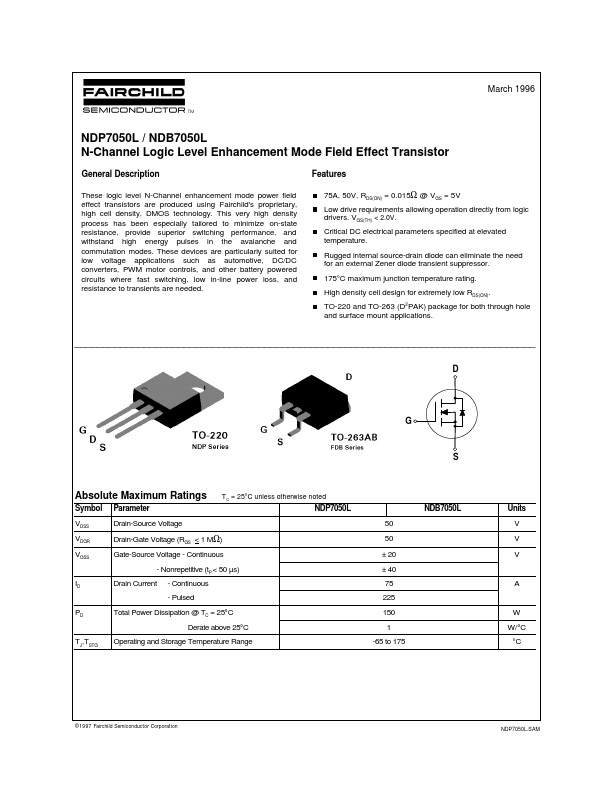

NDB7050L Overview

Key Specifications

Max Operating Temp: 175 °C

Description

These logic level N-Channel enhancement mode power field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulses in the avalanche and commutation modes.

Key Features

- 75A, 50V, RDS(ON) = 0.015Ω @ VGS = 5V Low drive requirements allowing operation directly from logic drivers

- Critical DC electrical parameters specified at elevated temperature

- Rugged internal source-drain diode can eliminate the need for an external Zener diode transient suppressor

- 175°C maximum junction temperature rating

- High density cell design for extremely low RDS(ON)