HM5225405B-75

Description

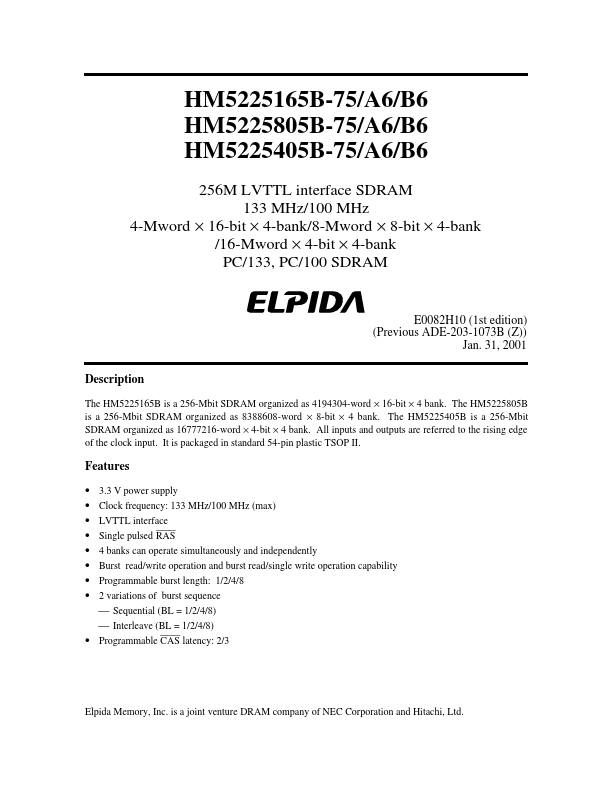

The HM5225165B is a 256-Mbit SDRAM organized as 4194304-word × 16-bit × 4 bank. The HM5225805B is a 256-Mbit SDRAM organized as 8388608-word × 8-bit × 4 bank. The HM5225405B is a 256-Mbit SDRAM organized as 16777216-word × 4-bit × 4 bank. All inputs and outputs are referred to the rising edge of the clock input. It is packaged in standard 54-pin plastic TSOP II.

Features

- -

- -

- -

- - 3.3 V power supply Clock frequency: 133 MHz/100 MHz (max) LVTTL interface Single pulsed RAS 4 banks can operate simultaneously and independently Burst read/write operation and burst read/single write operation capability Programmable burst length: 1/2/4/8 2 variations of burst sequence Sequential (BL = 1/2/4/8) Interleave (BL = 1/2/4/8)

- Programmable CAS latency: 2/3

Elpida Memory, Inc. is a joint venture DRAM pany of NEC Corporation and Hitachi, Ltd.

HM5225165B/HM5225805B/HM5225405B-75/A6/B6

- Byte control by DQM : DQM (HM5225805B/HM5225405B) : DQMU/DQML (HM5225165B)

- Refresh...