EBE41AE4ACFA

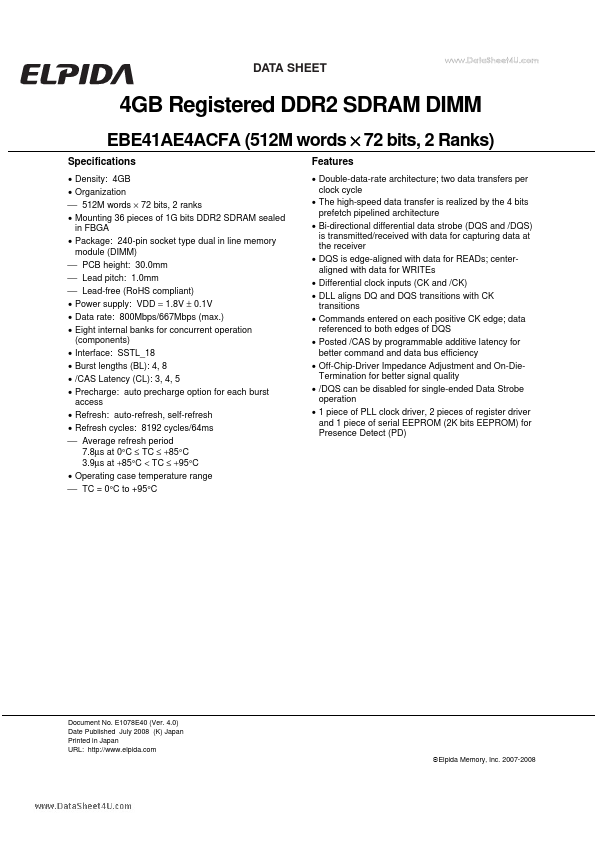

EBE41AE4ACFA is 4GB Registered DDR2 SDRAM DIMM manufactured by Elpida Memory.

Features

- Double-data-rate architecture; two data transfers per clock cycle

- The high-speed data transfer is realized by the 4 bits prefetch pipelined architecture

- Bi-directional differential data strobe (DQS and /DQS) is transmitted/received with data for capturing data at the receiver

- DQS is edge-aligned with data for READs; centeraligned with data for WRITEs

- Differential clock inputs (CK and /CK)

- DLL aligns DQ and DQS transitions with CK transitions

- mands entered on each positive CK edge; data referenced to both edges of DQS

- Posted /CAS by programmable additive latency for better mand and data bus efficiency

- Off-Chip-Driver Impedance Adjustment and On-Die Termination for better signal quality

- /DQS can be disabled for single-ended Data Strobe operation

- 1 piece of PLL clock driver, 2 pieces of register driver and 1 piece of serial EEPROM (2K bits EEPROM) for Presence Detect (PD)

Document No. E1078E40 (Ver. 4.0) Date Published July 2008 (K) Japan Printed in Japan URL: http://.elpida. Elpida Memory, Inc. 2007-2008

Ordering Information

Data rate Mbps (max.) 800 667 ponent 1 JEDEC speed bin- (CL-t RCD-t RP) DDR2-800 (5-5-5) DDR2-667 (5-5-5) 240-pin DIMM (lead-free) Gold Contact pad

..

Part number EBE41AE4ACFA-8E-E EBE41AE4ACFA-6E-E

Package

Mounted devices EDE1104ACSE-8E-E EDE1104ACSE-8E-E EDE1104ACSE-6E-E

Note: 1. Module /CAS latency = ponent CL + 1.

Pin Configurations

Front side 1 pin 64 pin 65 pin 120 pin

121 pin Back side

184 pin 185 pin

240 pin

Pin No. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

Pin name VREF VSS DQ0 DQ1 VSS /DQS0 DQS0 VSS DQ2 DQ3 VSS DQ8 DQ9 VSS /DQS1 DQS1 VSS /RESET NC VSS DQ10 DQ11 VSS DQ16 DQ17 VSS /DQS2

Pin No. 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87

Pin name A4 VDD A2 VDD VSS VSS VDD Par_In VDD A10 BA0 VDD /WE /CAS VDD /CS1 ODT1 VDD VSS DQ32 DQ33 VSS /DQS4 DQS4 VSS DQ34 DQ35

Pin No. 121 122 123 124 125 126 127 128 129 130 131...