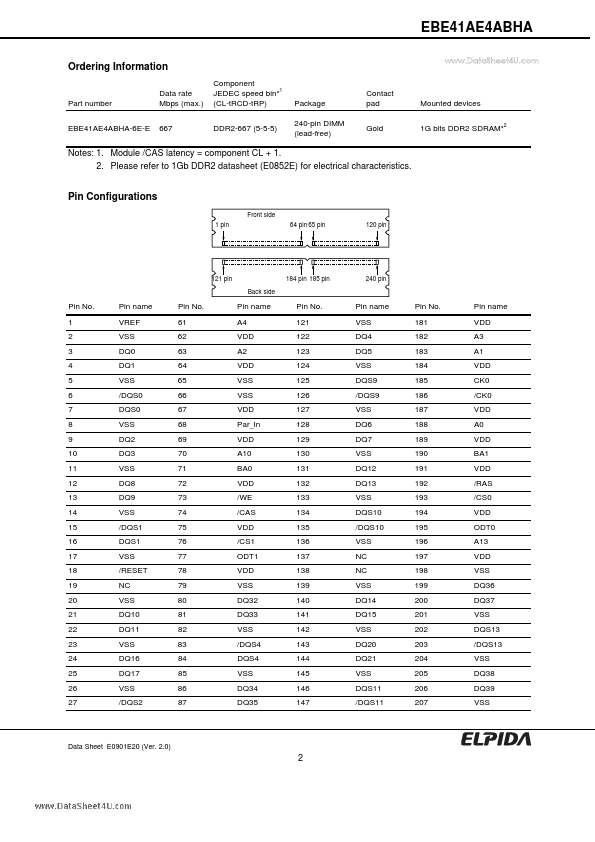

Datasheet Summary

DATA SHEET

..

4GB Registered DDR2 SDRAM DIMM

EBE41AE4ABHA (512M words × 72 bits, 2 Ranks)

Specifications

- Density: 4GB

- Organization 512M words × 72 bits, 2 ranks

- Mounting 36 pieces of 1G bits DDR2 SDRAM with sFBGA

- Package: 240-pin socket type dual in line memory module (DIMM) PCB height: 30.0mm Lead pitch: 1.0mm Lead-free (RoHS pliant)

- Power supply: VDD = 1.8V ± 0.1V

- Data rate: 667Mbps (max.)

- Eight internal banks for concurrent operation (ponents)

- Interface: SSTL_18

- Burst lengths (BL): 4, 8

- /CAS Latency (CL): 3, 4, 5

- Precharge: auto precharge option for each burst access

- Refresh: auto-refresh, self-refresh

- Refresh cycles: 8192...