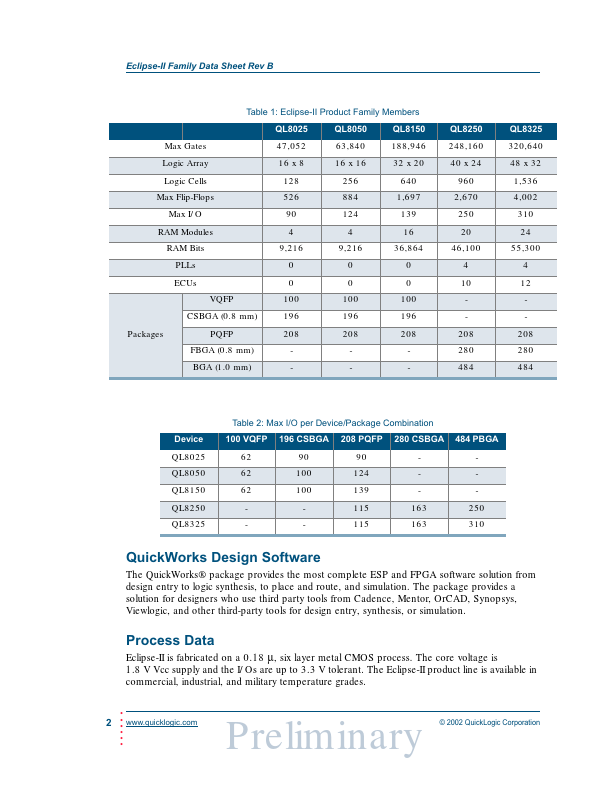

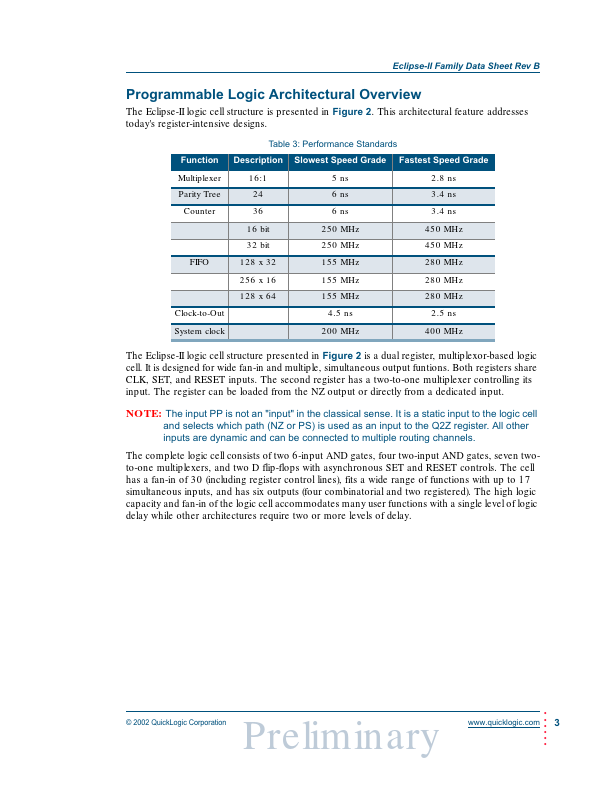

Datasheet Summary

(FOLSVH,, )DPLO 'DWD 6KHHW

/RZ 3RZHU )3- $ &RPELQLQJ 3HUIRUPDQFH 'HQVLW DQG (PEHGGHG 5$0

'HYLFH +LJKOLJKWV

)OH[LEOH 3URJUDPPDEOH /RJLF

0.18 µ, six layer metal CMOS process 1.8 V Vcc, 1.8/2.5/3.3 V drive capable I/O Up to 4,008 dedicated flip-flops Up to 55.3 K embedded RAM Bits Up to 313 I/O Up to 370 K system gates IEEE 1149.1 Boundary Scan Testing

$GYDQFHG &ORFN 1HWZRUN

Multiple dedicated Low Skew Clock

Networks High drive input-only networks Quadrant-based segmentable clock networks User Programmable Phase Locked Loops

(PEHGGHG &RPSXWDWLRQDO 8QLWV (&8V

Hardwired DSP building blocks with integrated Multiply, Add, and Accumulate Functions. pliant ...