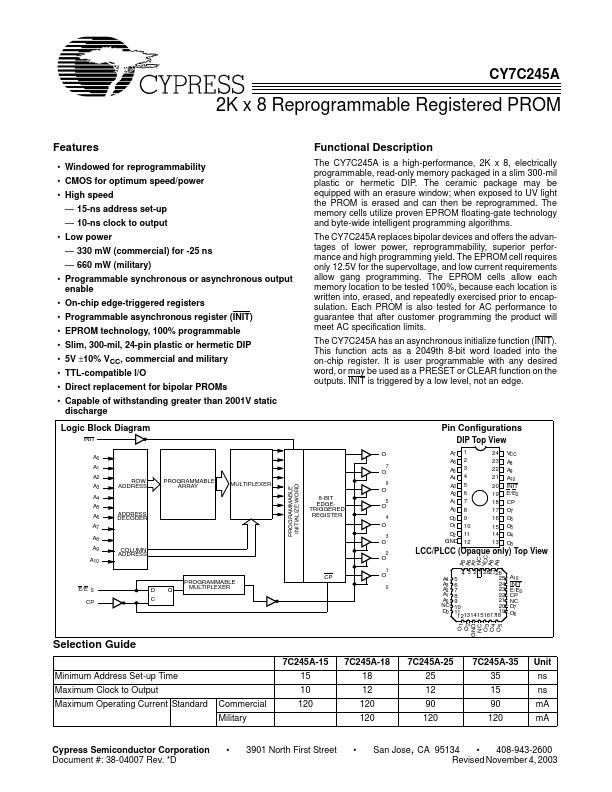

CY7C245A

Key Features

- Windowed for reprogrammability

- CMOS for optimum speed/power

- High speed - 15-ns address set-up - 10-ns clock to output

- Low power - 330 mW (commercial) for -25 ns - 660 mW (military)

- Programmable synchronous or asynchronous output enable

- On-chip edge-triggered registers

- Programmable asynchronous register (INIT)

- EPROM technology, 100% programmable

- Slim, 300-mil, 24-pin plastic or hermetic DIP

- 5V ±10% VCC, commercial and military