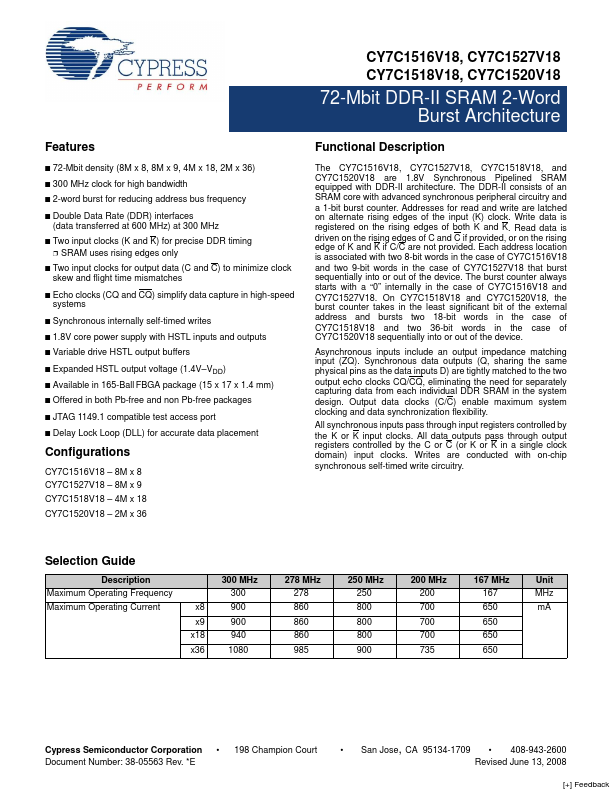

CY7C1527V18 Overview

Key Features

- 300 MHz clock for high bandwidth

- 2-word burst for reducing address bus frequency

- Double Data Rate (DDR) interfaces (data transferred at 600 MHz) at 300 MHz

- Two input clocks (K and K) for precise DDR timing ❐ SRAM uses rising edges only

- Two input clocks for output data (C and C) to minimize clock skew and flight time mismatches