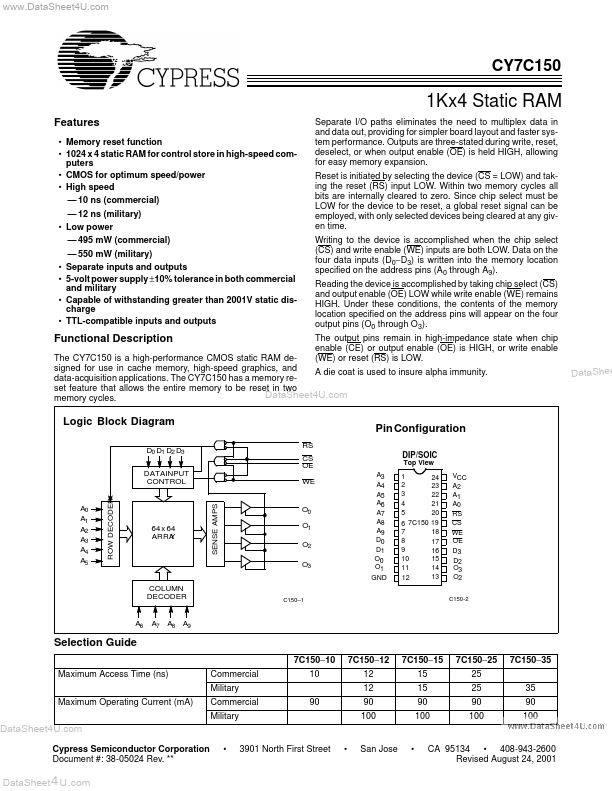

CY7C150 Overview

Key Specifications

Package: DIP

Operating Voltage: 5 V

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 4.5 V

Key Features

- Memory reset function

- 1024 x 4 static RAM for control store in high-speed computers

- CMOS for optimum speed/power

- 10 ns (commercial)

- 12 ns (military)