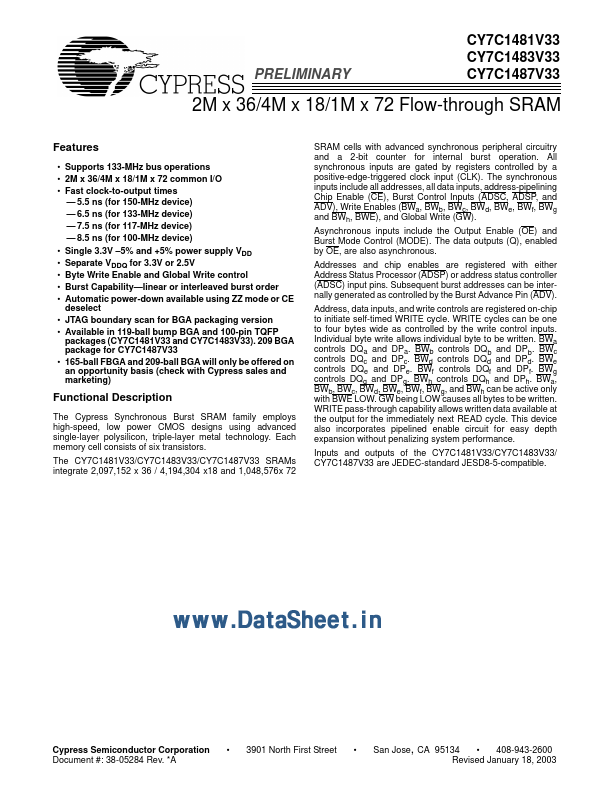

CY7C1483V33

Features

- Supports 133-MHz bus operations

- 2M x 36/4M x 18/1M x 72 mon I/O

- Fast clock-to-output times

- 5.5 ns (for 150-MHz device)

- 6.5 ns (for 133-MHz device)

- 7.5 ns (for 117-MHz device)

- 8.5 ns (for 100-MHz device)

- Single 3.3V

- 5% and +5% power supply VDD

- Separate VDDQ for 3.3V or 2.5V

- Byte Write Enable and Global Write control

- Burst Capability- linear or interleaved burst order

- Automatic power-down available using ZZ mode or CE deselect

- JTAG boundary scan for BGA packaging version

- Available in 119-ball bump BGA and 100-pin TQFP packages (CY7C1481V33 and CY7C1483V33). 209 BGA package for CY7C1487V33

- 165-ball FBGA and 209-ball BGA will only be offered on an opportunity basis (check with Cypress sales and marketing) SRAM cells with advanced synchronous peripheral circuitry and a 2-bit counter for internal burst operation. All synchronous inputs are gated by registers controlled by a positive-edge-triggered clock input (CLK). The synchronous inputs include all...