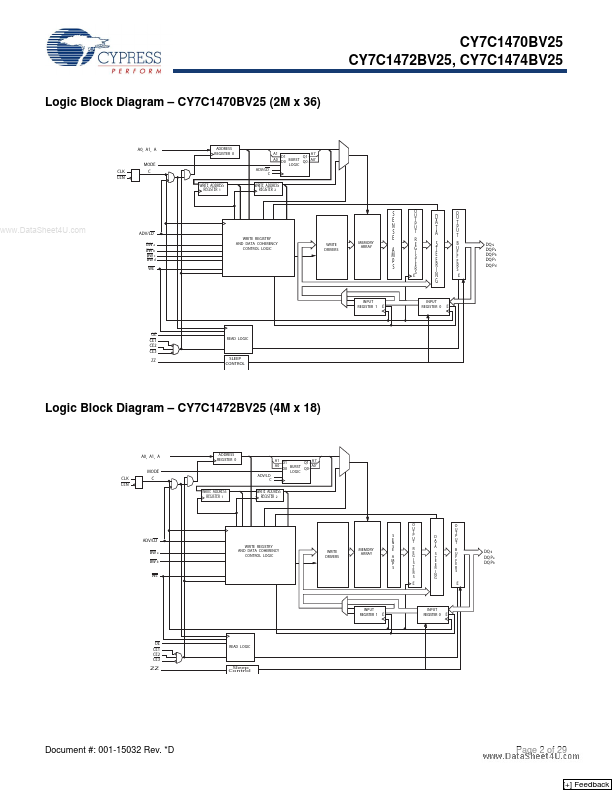

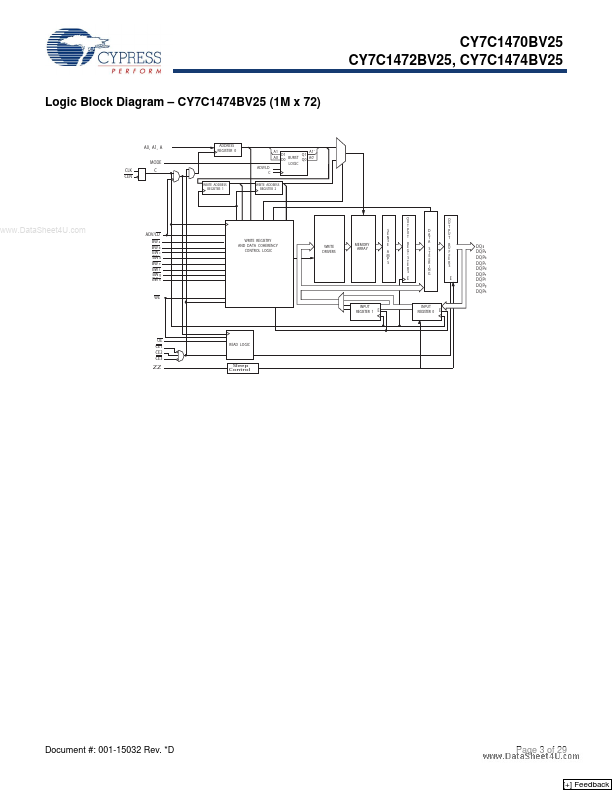

CY7C1474BV25 Overview

They are designed to support unlimited true back-to-back read or write operations with no wait states. The CY7C1470BV25, CY7C1472BV25, and CY7C1474BV25 are equipped with the advanced (NoBL) logic required to enable consecutive read or write operations with data being transferred on every clock cycle.

CY7C1474BV25 Key Features

- Functional Description

- Available speed grades are 250, 200, and 167 MHz Internally self-timed output buffer control to eliminate the need to us

- 198 Champion Court

- San Jose, CA 95134-1709

- 408-943-2600 Revised February 29, 2008