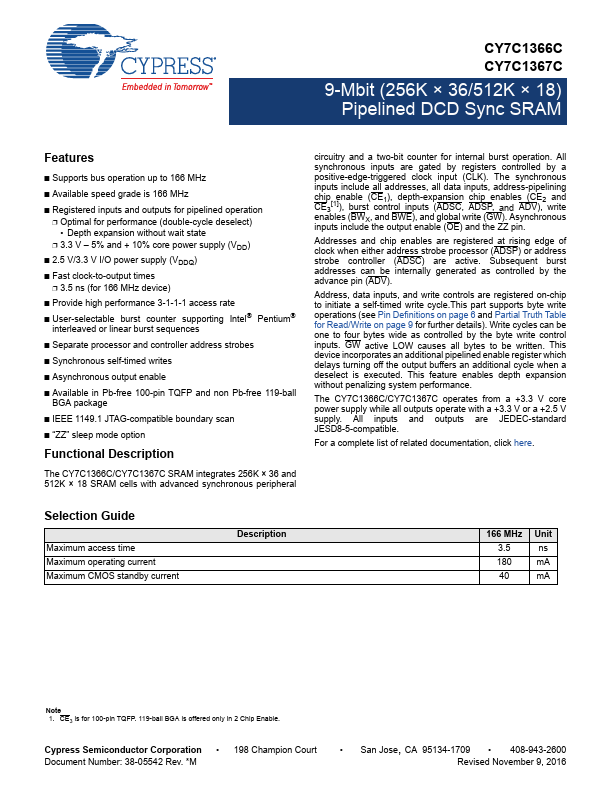

CY7C1367C Overview

Key Specifications

Package: LQFP

Mount Type: Surface Mount

Pins: 100

Operating Voltage: 3.3 V

Key Features

- Supports bus operation up to 166 MHz

- Available speed grade is 166 MHz

- Registered inputs and outputs for pipelined operation ❐ Optimal for performance (double-cycle deselect)

- Depth expansion without wait state ❐ 3.3 V – 5% and + 10% core power supply (VDD)

- 2.5 V/3.3 V I/O power supply (VDDQ)